電気電子系 News

トポロジカル絶縁体と磁気トンネル接合を集積した次世代不揮発性メモリSOT-MRAMの実証に成功

超低消費電力SOT-MRAMの実用化へ加速

概要

電子材料・物性グループのファム・ナム・ハイ准教授(電気電子コース 主担当)と米国カリフォルニア大学ロサンゼルス校のカン・ワン教授を中心とした国際研究チームは、トポロジカル絶縁体と磁気トンネル接合を集積したスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)素子の作製と、比較的高いトンネル磁気抵抗効果による読み出しおよびトポロジカル絶縁体による低電流密度の書き込みの実証に成功しました。

本研究成果は、10月29日付(英国時間)の英国の学術誌「Nature Communications」に掲載されました。

背景

SOT-MRAMは、スピンホール効果による純スピン流を用いて、高速で書き込みができる次世代の不揮発メモリ技術です。書き込み電流と電力を下げるためには、スピンホール効果が強いトポロジカル絶縁体を用いることが有望ですが、トポロジカル絶縁体と磁気トンネル接合との集積技術はこれまで確立されていませんでした。

今回の研究では、トポロジカル絶縁体と磁気トンネル接合を集積できることを示し、読み出しと書き込みの原理動作の実証に成功しました。本研究成果により、産業界を巻き込んだ超低消費電力SOT-MRAMの研究開発が加速されると期待できます。

研究成果

共同研究チームはSOT-MRAM素子の作製にあたって、分子線エピタキシャル結晶成長法を用いて製膜した(Bi,Sb)2Te3トポロジカル絶縁体、または工業生産に適するスパッタリング法を用いて製膜したBiSbトポロジカル絶縁体を下部電極に配置しました。さらにトポロジカル絶縁体と似た結晶構造を持つRu(5 nm)を中間層に、その上にCoFeB(2.5 nm)/ MgO(2 nm)/ CoFeB(5 nm)のMTJを製膜しました。次に、磁性層のCoFeBを結晶化させるために、250℃~300℃の温度で熱処理を行いました。最後に、3端子のSOT-MRAM素子を作製しました。

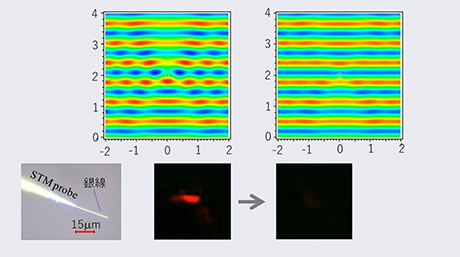

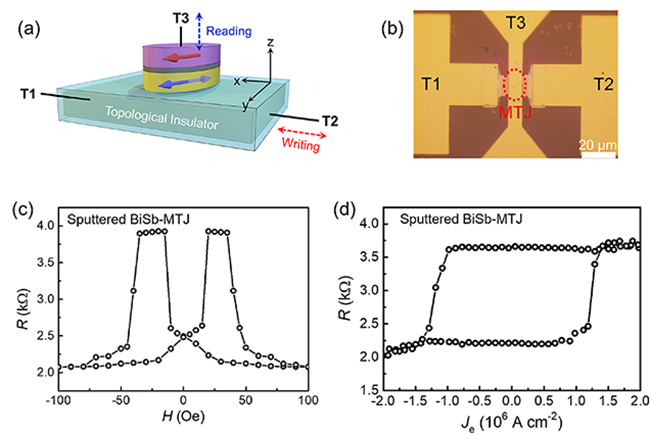

- 図1 (a)トポロジカル絶縁体とCoFeB/MgO/CoFeB磁気トンネル接合(MTJ)を集積した3端子SOT-MRAM素子の模型と(b)実際の素子の写真。(c)スパッタリング法のみで作製したBiSb-MTJ素子におけるトンネル磁気抵抗効果。(d)スピン軌道トルクによる書き込みの実証。

図1(a)と図1(b)には素子の模型と実際の素子の写真を示します。実際のSOT-MRAM素子サイズは4×8 μm2 ~ 100×200 nm2と小さいです。図1(c)にファム准教授のグループでスパッタリング法のみで作製したBiSbトポロジカル絶縁体-磁気トンネル接合のSOT-MRAM素子(1×3 μm2)におけるトンネル磁気抵抗効果を示します。この素子は、トポロジカル絶縁体を集積した磁気トンネル接合を250℃で熱処理したにもかかわらず、90%という比較的高い抵抗変化を達成しました。また、図1(d)に示すように、スピン軌道トルクによる低電流密度による書き込みに成功しました。

この実証実験により、トポロジカル絶縁体と磁気トンネル接合を集積でき、読み出しと書き込みの原理動作ができることを初めて示すことができました。

- 論文情報

| 掲載誌: | Nature Communications |

|---|---|

| 論文タイトル: | Magnetic memory driven by topological insulators |

| 著者: | Hao Wu, Aitian Chen, Peng Zhang, Haoran He, John Nance, Chenyang Guo, Julian Sasaki, Takanori Shirokura, Pham Nam Hai, Bin Fang, Seyed Armin Razavi, Kin Wong, Yan Wen, Yinchang Ma, Guoqiang Yu, Gregory P. Carman, Xiufeng Han, Xixiang Zhang, Kang L. Wang |

| DOI: | https://doi.org/10.1038/s41467-021-26478-3 |

- 巨大な一方向性スピンホール磁気抵抗効果を実証|東工大ニュース

- トポロジカル絶縁体で世界最高性能の純スピン注入源を開発|東工大ニュース

- スピン自由度を用いた次世代半導体デバイス実現へ大きな進展|東工大ニュース

- 半導体のパラダイムシフトを起こす「スピントロニクス」に賭ける — ファム・ナム・ハイ|研究ストーリー|研究

- Pham准教授が日本磁気学会の優秀研究賞を受賞|電気電子系News

- ファム・ナム・ハイ准教授がドイツ・イノベーション・アワード「ゴットフリード・ワグネル賞2019」を受賞|東工大ニュース

- PHAM NAM HAI RESEARCH GROUP

- ファム研究室 ―研究室紹介 #30―|電気電子系News

- すばらしい研究者の紹介 #4 -ファム ナム ハイ准教授-|電気電子系News

- 研究者詳細情報(STAR Search)- PHAM NAM HAI(ファム ナム ハイ)

- 電気電子コース(大学院課程)|教育|工学院 - 電気電子系

- University of California, Los Angeles(UCLA)

- King Abdullah University of Science and Technology

- 中国科学院

お問い合わせ先

東京工業大学 工学院 電気電子系

准教授 ファム・ナム・ハイ

E-mail : pham.n.ab@m.titech.ac.jp

Tel : 03-5734-3934 / Fax : 03-5734-3870