電気電子系 News

Beyond 5Gに向けた新規デジタル位相同期回路を開発

低ジッタと低スプリアスを同時に実現

要点

- デジタル位相同期回路の出力信号を高品質化する新方式を開発

- 新規カスケード型分数分周方式の採用により、スプリアスを大幅に低減

- 小型、低消費電力にIC実装可能であり、様々なBeyond 5G機器への適用を期待

概要

東京工業大学 工学院 電気電子系の岡田健一教授(電気電子コース 主担当)らの研究グループは、低スプリアス[用語1]と低ジッタ[用語2]を同時に実現する新方式のデジタル位相同期回路(PLL)[用語3]の開発に成功した。

無線通信機器などで広く用いられる分数分周PLL[用語4]では、原理的に出力信号に分周スプリアスが発生し、これを抑制する必要がある。従来のディザリング[用語5]と呼ばれる方法では、スプリアスは除去できるが、ジッタが増加する課題があった。また、デジタル非線形補償(DPD)[用語6]と呼ばれる方法では、PLLのロック時間が長くなるという課題があった。

今回の研究では、スプリアスが発生する周波数を帯域外の高周波にシフトし、除去するという新たな手法により、この課題を解決した。開発したPLLを、最小の配線半ピッチ(幅)65 nm(ナノメートル)のシリコンCMOSプロセス[用語7]で試作した。スプリアスの低減により10kHzから10MHzの範囲で積分したジッタとして143.7fsを実現した。消費電力は8.89mWであり、DPDを用いることなく、分周スプリアス-60dBcを達成したデジタルPLLの中で、最高のFoM[用語8]を達成した。このPLLは今後、小型で低消費電力、低位相雑音を重視するBeyond 5G機器向けSoCへの応用が期待される。

研究成果は、2月18日~22日に米国サンフランシスコで開催された「ISSCC 2024(国際固体素子回路会議)」で発表された。

開発の背景

Beyond 5G(B5G)では、スマートフォン等を用いて人が通信を行うだけでなく、交通、製造、医療など幅広い分野で、様々なIoT機器に無線通信機能やセンシング機能(例えばレーダーなど)が組み込まれる。IoT機器は、2030年代には1兆個にも達すると予想されているが、その実現には小型・低消費電力、低コスト化が不可欠であり、SoC(System on Chip)化が必須である。今回開発した位相同期回路(PLL:Phase-Locked Loop)は、無線通信やレーダーにおけるキーコンポーネントである。無線通信では局部発振器(Local Oscillator)に、レーダーではチャープ信号の生成などに用いられている。これらの応用において、PLLに要求される最も重要な性能指標の一つに位相雑音がある。位相雑音が大きいと、無線通信速度の低下やセンシング精度の低下につながる。そのため、SoCに集積可能で、低消費電力かつ低位相雑音を実現できるPLLの需要が高まっていた。

研究成果

PLLの位相雑音を増大させる要因には、ジッタやスプリアスがある。近年、携帯端末向けなどには、デルタシグマ変調(DSM:Delta-Sigma Modulation)[用語9]を用いた分数分周PLLが広く採用されている。最新の研究では、デジタル時間変換器(DTC:Digital-to-Time Converter)[用語10]を用いて、位相比較器(PD:Phase Detector)への入力信号の範囲を狭め、またDSMの量子化雑音を打ち消すことにより、さらなる低消費電力化と低位相雑音化を図る方式が提案されている。しかしながら、DTCが積分非直線性(INL:Integral Nonlinearity)[用語11]をもつため、誤差に周期性が生じ、それに起因するスプリアスが発生するという課題があった。

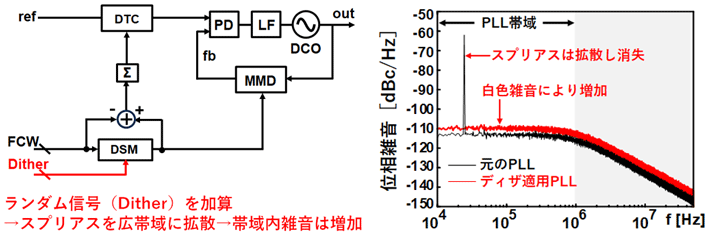

この課題に対して、図1(a)に示すような、信号経路にランダム信号を重畳する手法(ディザリング)が提案されている。これにより、誤差の周期性が崩れ、スプリアスのエネルギーが周波数軸に拡散する。ディザリングは、スプリアスを除去するのに有効であるが、ディザ信号自体が白色雑音であるため、帯域内の位相雑音が増加するという欠点があった。別の手法として、デジタル非線形補償(DPD:Digital Pre-Distortion)と呼ばれる技術もある。これは、DTCの非直線性をモデル化し、それを基にINLをデジタル信号処理で補正する技術である。この技術は、ジッタを増やすことなく、根本的にスプリアスを抑制することが可能であるが、デジタル信号処理に一定の時間を要するため、PLLの周波数が安定するまでの時間(ロック時間)が長くなるという欠点があった。

今回の研究で開発したPLLでは、(1)カスケード(縦列)型分数分周方式、(2)疑似差動型DTC、という2つの新しい回路技術を導入することにより、分数分周型のデジタルPLLにおいて、既存のDPD技術を使わずに、低ジッタと低スプリアス特性を実現した。

(1)カスケード型分数分周器

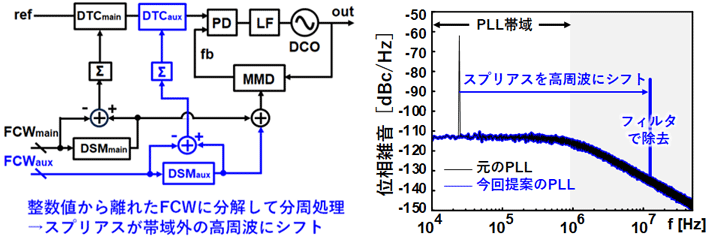

今回提案したカスケード型分数分周方式の構成と効果を図1(b)に示す。この構成では、元の周波数制御ワード(FCW)をFCWmainとFCWauxに分解し、それぞれDSMmainとDSMauxに供給してカスケードに分数分周を行う。DSMmainとDSMauxで発生する量子化雑音は、DTCmainとDTCauxでそれぞれ打ち消される。この時、FCWmainとFCWauxの分周比の分数部分が大きくなるよう分解するのがポイントである。分周スプリアスの周波数は、整数分周からのずれの大きさで決まるため、このように、FCWを分解して分数分周を行うことにより、ターゲット周波数から離れた高周波にスプリアスをシフトすることができる。PLLは、元々、低域通過特性を持つため、帯域外の高周波にシフトしたスプリアスは除去される。

(a)従来のディザリング方式

(b)今回提案のカスケード型分数分周方式

- 図1. 従来のディザリングと今回提案したカスケード型分数分周方式の比較

(2)疑似差動型DTC

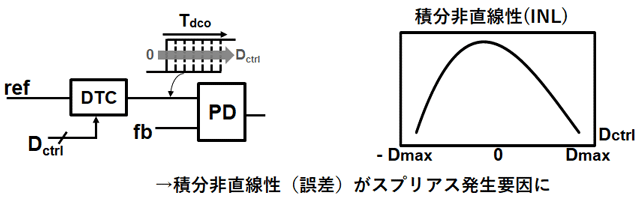

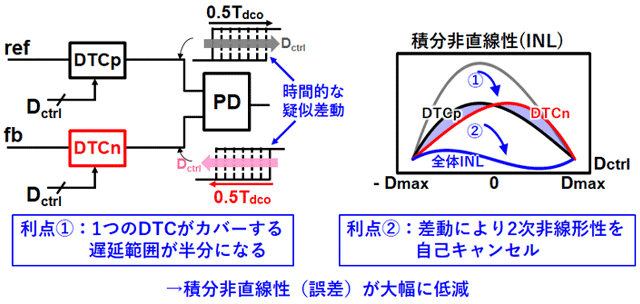

今回、開発したPLLのもう一つの特徴は、疑似差動型DTCである。DTCは、DSMに起因する量子化雑音を打ち消す働きを行い、その遅延範囲は、デジタル制御発振器(DCO:Digitally Controlled Oscillator)の1周期(Tdco)をカバーする必要がある。従来のDTC設計では、消費電力、遅延範囲、雑音とのトレードオフのため、図2(a)に示すように一定量のINLが発生し、これが誤差となり、量子化雑音の低減効果に制約があった。今回開発した疑似差動型DTCでは、図2(b)に示すように、位相比較器の入力にDTCpとDTCnの2つの同じDTCを配置する。DSMからの量子化雑音が増加すると、DTCpの遅延は増加する一方、DTCnの遅延は減少するため、時間領域で擬似的な差動動作を行う。結果、提案したDTCのINLは、等価的にDTCpとDTCnのINLの差になり、大幅に小さくなる。さらに、DTCpとDTCnに必要な遅延範囲が半分になるため、INLは本質的に小さくなり、より強力にスプリアスを低減できる。

(a)従来のDTC

(b)今回提案した疑似差動型DTC

- 図2. 従来のデジタル時間変換器(DTC)と今回提案した疑似差動型DTCの比較

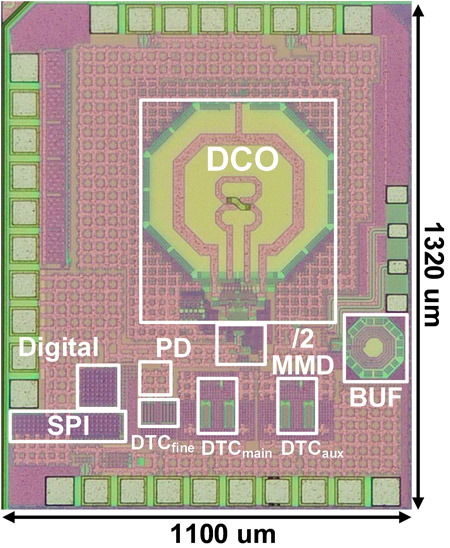

新たに提案したカスケード型分数分周方式と疑似差動型DTCを採用したデジタルPLL回路を、65 nmのCMOSプロセスを用いて実際に作製した(図3)。チップサイズは1.3 mm x 1.1 mmである。作製したPLL回路を評価した結果、10kHzから10MHzで積分したジッタは、元の243.5fsから143.7fsまで低減できることを確認した。これは、提案したカスケード型分数分周方式を適用することで、分周スプリアスが低減した効果によるものである。また、消費電力は8.89 mWであり、DPDを用いずに分周スプリアス-60dBcを達成したデジタルPLLの中で最高のFoM(Figure of Merit)を達成した。

図3. 作製したPLL回路のチップ写真

社会的インパクト

来るべきSociety 5.0では、実世界(フィジカル空間)の膨大なセンシングデータをサイバー空間との間で通信する。Beyond 5Gは、こうした社会を支える中核的なインフラの役割を担うものである。本研究では、デジタル回路向けの微細CMOSプロセスとの親和性が高く、小型・低消費電力にSoC集積可能なデジタルPLL構成により、位相雑音の低い高性能なPLLを実現している。これにより、IoT機器の小型・低消費電力、低コスト化が可能となり、Beyond 5GにおけるIoTサービスの普及に貢献するものである。

今後の展開

本研究成果をさらに進め、さらなる高性能なPLLを実現するアーキテクチャや回路を探求するとともに、Beyond 5G無線通信機やレーダーなど実際のアプリケーションでの効果も実証していく。

- 付記

本研究は、国立研究開発法人情報通信研究機構(NICT)の委託研究「継続的進化を可能とするB5G IoT SoC及びIoTソリューション構築プラットホームの研究開発」(JPJ012368C00801)の成果の一部である。

- 用語説明

[用語1] スプリアス(Spurious) : 意図して出力する信号以外の不要な信号。

[用語2] ジッタ(Jitter) : 信号の立ち上がりまたは立ち下りタイミングが揺らぐ現象。本来のタイミングからのずれが統計的にどれぐらいの幅を持つかで評価する。

[用語3] 位相同期回路(PLL : Phase-Locked Loop) : 集積回路中では正確な周波数基準が作れないため、水晶発振器による基準周波数f refを元に、それをN逓倍して所望周波数N・f refの周波数の信号を得るための回路。

[用語4] 分数分周PLL(Fractional-N PLL) : PLLには、整数分周型と分数分周型がある。整数分周型PLLでは基準信号に対して整数倍の周波数を出力するが、分数分周型では分数倍の任意の周波数の出力が可能である。無線通信やレーダー用途には、分数分周PLLが必要である。

[用語5] ディザリング(Dithering) : 信号にランダムなノイズを加えることにより、誤差を拡散させる技術。

[用語6] デジタル非線形補償(DPD:Digital Predistortion) : 信号の非線形性を補償するための技術。対象となる回路の非線形性をモデル化し、その逆特性の信号を入力することで、線形な出力信号を得る。

[用語7] CMOSプロセス : N型とP型のMOSFETを相補的に用いた集積回路であり、バイポーラプロセスと比較して消費電力の削減と高い集積率を実現したプロセスである。近年の集積回路はほぼすべてがCMOSプロセスとなっている。

[用語8] FoM (Figure of Merit) : 消費電力で規格化したジッタ性能を示す。ジッタと消費電力はトレードオフの関係にあり、発振器の消費電力を増やすとジッタが減少し、消費電力を減らすとジッタが増加する。

[用語9] デルタシグマ変調(Delta-Sigma Modulation) : 信号の大きさをパルスの密度で表現するパルス密度変調の一種。信号帯域よりも十分高いサンプリング周波数により標本化(オーバーサンプリング)を行い、帰還回路によって、量子化雑音の分布を制御できる(ノイズシェーピング)のが特徴。

[用語10] デジタル時間変換器 (DTC : Digital-to-Time Converter) : デジタル制御値により、遅延時間が変化する可変遅延回路。

[用語11] 積分非直線性(INL: Integral Nonlinearity) : デジタル制御値入力に対する理想的な出力値と実際の出力値の誤差。

- 研究成果発表

この成果は2月18日~22日にサンフランシスコで開催された「2024 IEEE International Solid-State Circuits Conference (ISSCC 2024) : 2024年米国電気電子学会 国際固体素子回路会議」で発表された。

| 講演セッション : | Session 10 –Frequency Synthesis |

| 講演時間 : | 現地時間2月20日午前8時50分 |

| 講演タイトル : | A 7GHz Digital PLL with Cascaded Fractional Divider and Pseudo-Differential DTC Achieving -62.1dBc Fractional Spur and 143.7fs Integrated Jitter |

| ISSCC会議情報 : | IEEE International Solid-State Circuits Conference (ISSCC) |

| 講演セッション : | Session 10 –Frequency Synthesis |

| 講演時間 : | 現地時間2月20日午前8時50分 |

| 講演タイトル : | A 7GHz Digital PLL with Cascaded Fractional Divider and Pseudo-Differential DTC Achieving -62.1dBc Fractional Spur and 143.7fs Integrated Jitter |

| ISSCC会議情報 : | IEEE International Solid-State Circuits Conference (ISSCC) |

- オールCMOSの300 GHz帯フェーズドアレイ送信機を開発|東工大ニュース

- 300GHz帯でのビームフォーミングと高速データ伝送に成功|東工大ニュース

- 6G向け100 Gbps超の超高速サブテラヘルツフェーズドアレイ無線機を開発|東工大ニュース

- 低軌道衛星コンステレーションに向けた耐放射線Ka帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 小型地球観測衛星搭載用のKa帯フェーズドアレイ無線機の低消費電力化に成功|東工大ニュース

- 新アーキテクチャのデジタル位相同期回路を開発|東工大ニュース

- Beyond 5Gの端末機に向けたマルチバンドフェーズドアレイ受信ICを開発|東工大ニュース

- 超小型衛星搭載用Ka帯無線機の開発に成功|東工大ニュース

- 無線電力伝送と無線通信双方に同時対応するミリ波帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 5GおよびBeyond 5Gの基地局に向けた高効率ミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 超高速ビームフォーミングが可能なミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 電源不要のミリ波帯5G無線機の開発に成功|東工大ニュース

- テラヘルツ帯でのフェーズドアレイ無線機を実現|東工大ニュース

- 300 GHz帯無線トランシーバの省電力化に成功|東工大ニュース

- Ka帯衛星通信向け無線ICの開発に成功|東工大ニュース

- 偏波MIMO対応ミリ波フェーズドアレイ無線機を開発|東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ — 岡田健一|研究ストーリー|研究

- 岡田健一教授にIEEE Fellow(フェロー)の称号授与|電気電子系News

- 「異分野融合研究支援」を創設 3チームに授与|東工大ニュース

- 岡田健一 Kenichi Okada|研究者検索システム 東京工業大学STARサーチ

- 岡田研究室

- 電気電子コース(大学院課程)|教育|工学院 電気電子系

- 電気電子系(学士課程)|教育|工学院 電気電子系

- 研究成果一覧