電気電子系 News

オールCMOSの300 GHz帯フェーズドアレイ送信機を開発

100 Gbps超のデータ速度を達成、6G無線機の実現へ大きく前進

要点

- 6Gでの実用化が期待される300 GHz帯フェーズドアレイ送信機を安価で量産性に優れたCMOS集積回路により実現

- 300 GHz帯増幅器、アンテナおよびビームフォーマをオールCMOSの同一チップ上に集積することに世界で初めて成功

- 16×4の2次元フェーズドアレイ送信機を開発、100 Gbps超のデータ速度を達成

概要

東京工業大学 工学院 電気電子系の岡田健一教授(電気電子コース 主担当)らと日本電信電話株式会社の研究グループは、テラヘルツ帯[用語1]で通信が可能なアクティブフェーズドアレイ[用語2]送信機を、アンテナや電力増幅器を含めすべてCMOS集積回路で実現することに世界で初めて成功した。安価で量産が可能なシリコンCMOSプロセスチップによる300 GHz帯の無線機実現が可能となり、100 Gbps超の次世代無線通信システムの実現を大きく進展させることができた。

今回開発したテラヘルツ送信機は64系統の送信回路を持ち、それらすべてを電気的に制御することにより16×4の2次元フェーズドアレイ動作が可能である。このCMOS送信回路を実際に評価したところ、108 Gbpsの送信レートが実証できた。量産性に優れたCMOS集積回路で300 GHz帯の無線伝送が可能となり、同周波数帯を用いた次世代高速6G[用語3]無線機の実現・普及を大きく加速させることが期待される。

研究成果は、2月18日~22日に米国サンフランシスコで開催された「ISSCC 2024(国際固体素子回路会議)」で発表された。

開発の背景

300 GHz帯は利用可能な広大な周波数帯域が残されていることから、100 Gbps以上の超高速6G無線通信サービスの実用化が期待されている。しかしながらこのような高い周波数では、空間伝搬損失を補うだけの十分高い送信電力を有する送信機の実現が課題となっている。この課題を解決するために、複数のアンテナの出力を合成・制御することでアンテナ利得を高めビームステアリング[用語4]を可能にする、2次元フェーズドアレイ技術の研究が進められてきた。しかし十分な送信電力を確保するためには、それぞれの送信回路の出力電力を確保する必要がある。フェーズドアレイは多くの送信回路を必要とするため、安価で量産性・集積化に優れるシリコンCMOSプロセスの活用が非常に有効であるが、シリコンCMOSプロセスによるトランジスタの動作周波数の制限から、これまでこの周波数帯で高性能の電力増幅器を実現することは一般的には困難であった。

そこで、CMOS集積回路ではミキサや逓倍器から直接アンテナを駆動する回路方式が検討されてきたが、十分な出力電力が得られないために電力効率が下がり、またチップ面積が大きくなるなど、面積効率・コストの観点からも十分なものではなかった。すなわち、電力増幅器が搭載されていないこれまでの300 GHz帯フェーズドアレイICでは十分な性能が得られていなかった。そのため、300 GHz帯においても電力増幅器でアンテナを駆動するCMOSフェーズドアレイICの実現が大きく期待されていた。

研究成果

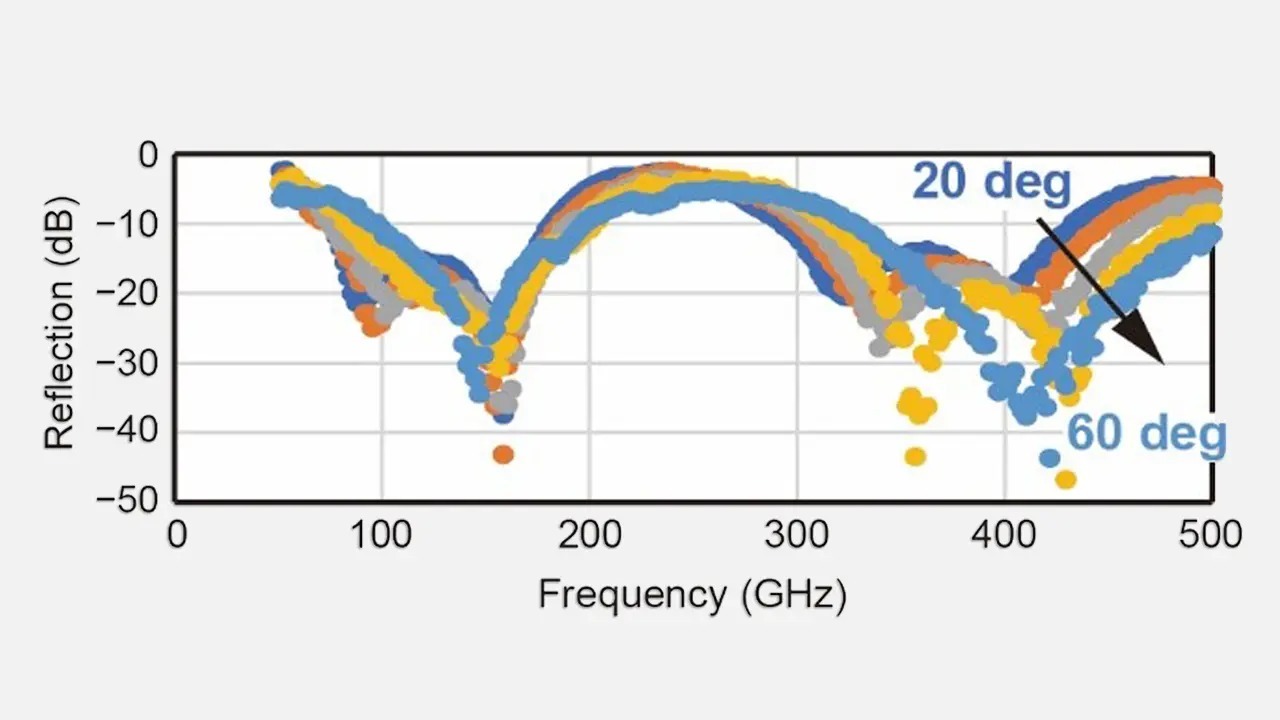

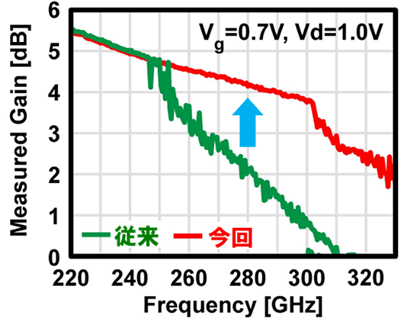

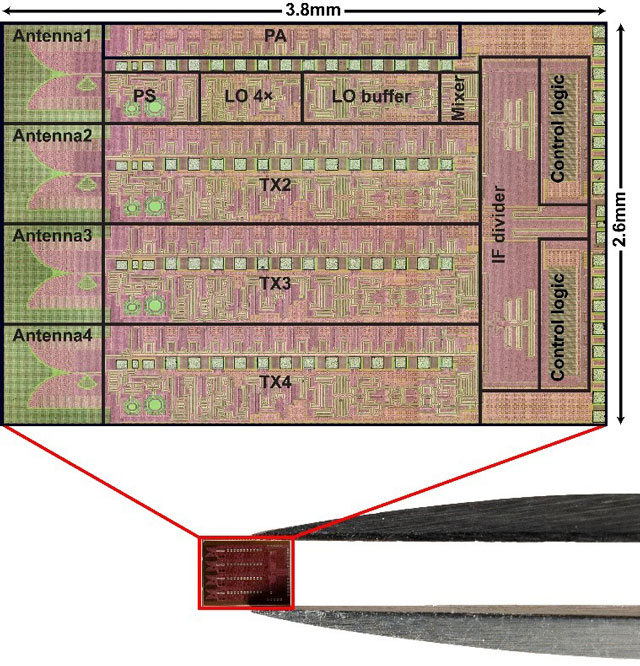

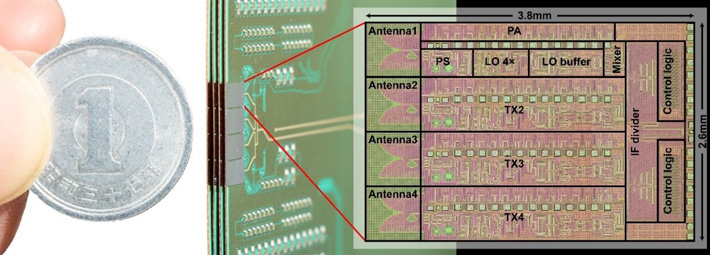

今回の研究で開発した300 GHz帯フェーズドアレイ送信機は65 nmのシリコンCMOSプロセスを用いて設計した。CMOSでも300 GHz帯で動作する電力増幅器を実現するために、基本となるトランジスタのレイアウトを新たに最適化した。その結果、レイアウト最適化による寄生抵抗・容量の低減により、250-300 GHz帯での利得が従来に比べて大きく向上した(図1)。これにより、300 GHz帯での電力増幅器の設計が可能となった。本トランジスタを用いて設計した増幅器は、237-267 GHzで20 dB以上の利得を有し、251 GHzで-3.4 dBmの飽和出力電力を達成した。また、300 GHz帯雑音評価系を構築して増幅器の雑音測定を行い、雑音指数実測値15 dBが得られた。送信機ICには、本トランジスタを用いた電力増幅器でオンチップのアンテナを直接駆動する増幅器ラストの構成[用語5]を採用した。また、サブハーモニックミキサ、移相器、4逓倍器付きのLO回路の構成を工夫し、従来の5分の1の面積に小型化することに成功し、4系統の送信回路を3.8 mm×2.6 mmの1チップに集積した。

図1. 従来のCOMSトランジスタとレイアウト最適化後のトランジスタの利得の比較

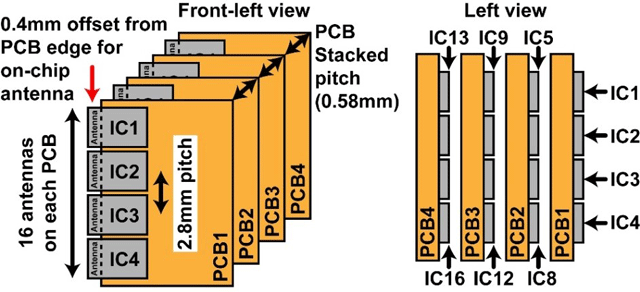

次に実際に、65 nmシリコンCMOSプロセスを用いて300 GHz帯送信機ICチップを作製した(図2)。このチップのアンテナ部は、イオン照射により基板を高抵抗化することで、損失を低減している。この4系統の送信回路を有するCMOS ICチップをプリント基板上に4つ並べて実装することで、16アレイのフェーズドアレイ送信機を構成した。さらにこの基板を4枚重ねて張り合わせることで、16×4の2次元フェーズトアレイ送信機を実現した(図3)。ICチップは50 μmに薄化して基板共振の影響を最小化すると同時に、基板からアンテナ部を0.4 mm飛び出す形で実装することでオンチップアンテナの放射信号の反射の影響を低減している(図4)。

図2. 作成した300 GHz帯送信機ICのチップ写真

図3. フェーズドアレイ送信機の基板構成

図4. フェーズドアレイ送信機の写真(チップ実装部)

開発した送信機の性能評価のために、オンチップアンテナを除いた1系統の送信回路の送信レートを高周波プローブにより測定したところ、16QAM[用語6]変調時に108 Gbps、32QAM[用語7]変調時に95 Gbpsとなり、100 Gbpsを超える送信レートが確認できた。また、50 cmの距離での4系統の送信回路によるアンテナビームパターンは、120°の角度掃引において設計値と非常によく一致し、フェーズドアレイ動作が可能であることが確認できた。

社会的インパクト

本研究で開発されたテラヘルツ帯フェーズドアレイ送信機はアンテナを含め全てCMOS集積回路で実現している。安価で量産性に優れたCMOSプロセスで300 GHz帯の送信機を世界で初めて実現できたことで、同周波数帯を用いた6G高速無線機の実現に大きく貢献することが期待できる。

今後の展開

今後は本研究をさらに進め、より多くの送信回路を集積化したより大規模なフェーズドアレイ送信機の開発を目指す。そうした送信機によって、さらに長距離での超高速無線通信が可能となり、300 GHz帯の基地局等への展開を通して、6G高速無線システムの普及に貢献することができる。

- 用語説明

[用語1] テラヘルツ帯 : 5Gなどで用いられるミリ波帯より高い、300 GHzから3,000 GHz(3 THz)の周波数帯。テラヘルツ帯を用いる通信規格としてはIEEE802.15.3dが知られている。IEEE802.15.3dでは252-325 GHzの周波数帯を用いるため、252-300 GHzの周波数帯も含めて広義にテラヘルツ帯と呼ばれることが多い。

[用語2] フェーズドアレイ : 複数のアンテナへ位相差をつけた信号を給電する技術。ビームステアリングの実現に利用される。

[用語3] 6G : 第6世代移動通信システム。第5世代移動通信システム(5G)の次の世代の移動通信システム。

[用語4] ビームステアリング : アンテナの指向性パターンを制御する技術。通常、フェーズドアレイを用いて電気的に制御する。

[用語5] 増幅器ラストの構成 : 送信回路において、最終出力段が電力増幅器となっている構成。通常最終出力段はアンテナなどの駆動電力を得るために電力増幅器が用いられるが、CMOSプロセスでは300 GHz帯のような高い周波数での電力増幅器の実現が難しく、これまでの研究開発報告では、ミキサや逓倍器が最終段となるミキサラスト構成や、逓倍器ラスト構成が用いられており、増幅器が最終段となる増幅器ラスト構成はこれまで実現されていなかった。

[用語6] 16QAM : 16 Quadrature Amplitude Modulationの略。搬送波の振幅および位相変化の16値を用いる変調方式。

[用語7] 32QAM : 32 Quadrature Amplitude Modulationの略。搬送波の振幅および位相変化の32値を用いる変調方式。

- 研究成果発表

この成果は2月18日~22日にサンフランシスコで開催された「2024 IEEE International Solid-State Circuits Conference (ISSCC 2024) : 2024年米国電気電子学会 国際固体素子回路会議」で発表された。

| 講演セッション : | Session 24 –D-Band/Sub-THz Transmitters and Sensors |

| 講演時間 : | 現地時間2月21日午前10時55分 |

| 講演タイトル : | A 236-to-266GHz 4-Element Amplifier-Last Phased-Array Transmitter in 65nm CMOS |

| ISSCC会議情報 : | IEEE International Solid-State Circuits Conference (ISSCC) |

- Beyond 5Gに向けた新規デジタル位相同期回路を開発|東工大ニュース

- 300GHz帯でのビームフォーミングと高速データ伝送に成功|東工大ニュース

- 6G向け100 Gbps超の超高速サブテラヘルツフェーズドアレイ無線機を開発|東工大ニュース

- 低軌道衛星コンステレーションに向けた耐放射線Ka帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 小型地球観測衛星搭載用のKa帯フェーズドアレイ無線機の低消費電力化に成功|東工大ニュース

- 新アーキテクチャのデジタル位相同期回路を開発|東工大ニュース

- Beyond 5Gの端末機に向けたマルチバンドフェーズドアレイ受信ICを開発|東工大ニュース

- 超小型衛星搭載用Ka帯無線機の開発に成功|東工大ニュース

- 無線電力伝送と無線通信双方に同時対応するミリ波帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 5GおよびBeyond 5Gの基地局に向けた高効率ミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 超高速ビームフォーミングが可能なミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 電源不要のミリ波帯5G無線機の開発に成功|東工大ニュース

- テラヘルツ帯でのフェーズドアレイ無線機を実現|東工大ニュース

- 300 GHz帯無線トランシーバの省電力化に成功|東工大ニュース

- Ka帯衛星通信向け無線ICの開発に成功|東工大ニュース

- 偏波MIMO対応ミリ波フェーズドアレイ無線機を開発|東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ — 岡田健一|研究ストーリー|研究

- 岡田健一教授にIEEE Fellow(フェロー)の称号授与|電気電子系News

- 「異分野融合研究支援」を創設 3チームに授与|東工大ニュース

- 岡田健一 Kenichi Okada|研究者検索システム 東京工業大学STARサーチ

- 岡田研究室

- 電気電子コース(大学院課程)|教育|工学院 電気電子系

- 電気電子系(学士課程)|教育|工学院 電気電子系

- 日本電信電話株式会社(NTT)

- 研究成果一覧