電気電子系 News

5 nm CMOSプロセス対応可能な先端MRAM技術を開発

MRAMの微細化を加速

Pham研究室の張 瑞顕さん、加々美 尚さん(博士課程)と伊藤 大起さん(修士課程)は 半導体ファウンドリーを先駆けて5 nm CMOS プロセス対応可能な先端MRAM技術の開発に成功した。現在のMRAMはCMOS 14~16 nm対応にとどまっている。これより微細化すると、磁性体の熱揺らぎによって、データの保存能力が低下する。より微細なCMOSプロセス対応可能なMRAM素子を実現するためには、より高い垂直磁気異方性を実現する必要がある。現在に半導体ファウンドリー各社が先端MRAMの開発のしのぎを削っている。たとえば、TSMCがヨーロッパに研究所を設置し、5 nm CMOSプロセス対応なMRAM技術の開発を目指している。また、サムスンも2027年に5 nm CMOSプロセス対応なMRAM技術の確立を目指している。

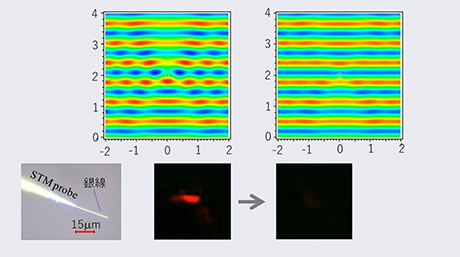

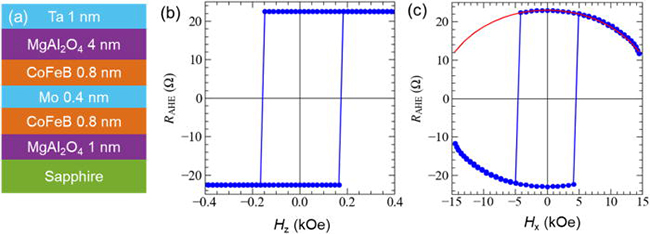

図(a)5 nm CMOSプロセス対応可能な2重CoFeB構造、

(b)垂直磁界および(c)面内磁界を印加した時の異常ホール抵抗(~磁化垂直成分)の曲線。

本研究では、独自に開発したMo/B-rich CoFeB/MgAl2O4構造を採用することによって、300℃~400℃熱処理後に、B(ボロン)を絶妙に磁性層に残し、低い磁化を実現することで、巨大な垂直異方性磁界Hk ~ 17.5 – 19.5 kOe (従来の3倍)および巨大な垂直磁気異方性エネルギーKeff ~ 6.9 – 9.4×106 erg/cc(従来の2倍)を実現した。その結果、MRAM素子サイズを22 nmまで低減できるため、 7 nm CMOSプロセスに対応できるようになった。さらに、2重CoFeB層(図a~c)を用いることで、MRAM素子サイズを14.5 nmまで微細化可能となり、より先端な5 nm CMOS プロセスを対応可能となった。

本研究成果は、2025年12月10日付(米国時間)の米国の学術誌「Applied Physics Letters」に掲載された。

論文情報

論文タイトル:

Giant perpendicular magnetic anisotropy in Mo/Boron-rich CoFeB/MgAl2O4 structure

著者:

Zhang Ruixian, Sho Kagami, Daiki Ito, Quang Le, Brian York, Cherngye Hwang, Xiaoyong Liu, Son Le, Maki Maeda, Tuo Fan, Yu Tao, Hisashi Takano, Pham Nam Hai