電気電子系 News

Beyond 5Gに向けた新型デジタル送信機CMOS ICを開発

低消費電力が求められるIoT機器への応用に期待

ポイント

- 高電力効率と線形性を両立する無線通信用送信機CMOS ICを開発

- 複雑なコーディックを使用しない新しいデジタル送信機のアーキテクチャを提案

- 小型・低消費電力でさまざまなIoT機器に搭載可能であり、IoTの普及に貢献

概要

東京科学大学(Science Tokyo)※ 工学院 電気電子系の岡田健一教授、張雲程助教(ともに電気電子コース 主担当)らの研究チームは、高い電力効率と線形性を備えた無線通信用送信機CMOS ICを開発しました。

無線通信機器において、アンテナに信号を送信する電力増幅器(PA)を含む送信機は、最も消費電力が大きい部品の一つです。そのため高い電力効率が求められますが、従来のアナログPA[用語1]では、電力効率と線形性の間に原理的なトレードオフが存在していました。

今回研究チームはこの課題を克服するため、デジタルPA[用語2]を活用した新しい送信機ICを開発しました。この送信機ICでは、高効率な1ビットデジタルPAを制御するポーラ変調[用語3]信号を、複雑なCORDIC(コーディック)[用語4]を使用せずに生成する新しいアーキテクチャを採用しています。この新アーキテクチャによるデジタルポーラ変調送信機ICを、65 nm(ナノメートル)のシリコンCMOSプロセス[用語5]で試作したところ、低出力領域の電力効率はアナログPAと比較して約1.8倍向上しました。また、変調信号による評価でもシステム要求を満足する線形性を確認でき、今回開発した送信機ICが高効率と高線形性を両立する優れた方式であることが実証されました。この送信機ICは今後、低消費電力や高線形性が求められるBeyond 5G IoT機器向けSoCへの応用が期待されます。

本成果は、2月16日~20日に米国サンフランシスコで開催された「ISSCC 2025(国際固体素子回路会議)」で発表されました。

※2024年10月1日に東京医科歯科大学と東京工業大学が統合し、東京科学大学(Science Tokyo)となりました。

背景

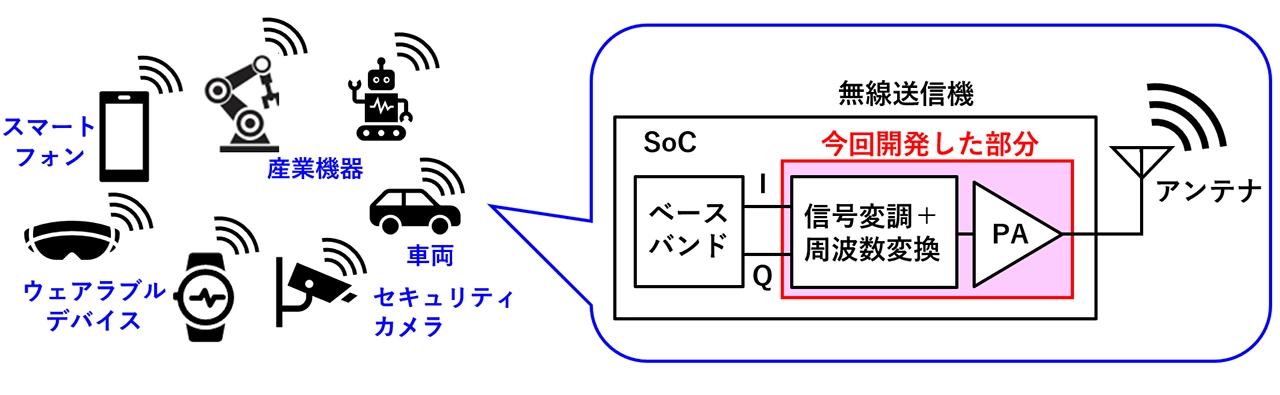

Beyond 5G(B5G)では、スマートフォン等を用いて人が通信を行うだけでなく、交通、製造、医療、セキュリティなど多岐にわたる分野において、さまざまなIoT機器に無線通信機能が組み込まれます(図1)。IoT機器は、2030年代には1兆個にも達すると予想されていますが、その実現には小型・低消費電力化と低コスト化が不可欠であり、これらを実現するにはSoC(システム・オン・チップ)[用語6]化が必須となります。

そうしたIoT機器では、低電力レベルの入力信号を、無線通信システムが要求する電力レベルまで増幅し、送信用アンテナに送るために電力増幅器(PA)が用いられます(図1)。PAは、無線通信機において最も消費電力の大きい部品の一つであり、高い電力効率が求められます。また、近年の無線通信システムで採用されている変調方式では、信号に高い線形性が要求されており、PAは信号を増幅する際にその線形性を維持する必要があります。しかし従来のアナログPAでは、電力効率と線形性の間に原理的なトレードオフが存在しました。そのため、小型で低消費電力なIoT通信機の実現に向けて、SoCに集積可能で、高電力効率かつ高線形なPAとそれを用いた送信機の開発が求められています。

図1.さまざまなIoT機器に無線送信機が組み込まれる

今回の研究ではこうした背景を踏まえて、デジタルPAを用いた送信機を開発しました。デジタルPAは、インバータ構成によるオン/オフのスイッチング動作を利用して信号を増幅するため、原理的に定常電流が流れず、アナログPAに比べて非常に高い電力効率を実現できます。また、オン/オフの2状態のみであるため、トランジスタの線形性に依存せず、入力信号を適切なデジタル変調信号に変換することで、信号歪を抑えることが可能です。こうした特長があるデジタルPAは、高電力効率と高線形性のトレードオフを打破することができる有望な方式です。デジタル送信機のアーキテクチャは、直交変調[用語7]とポーラ(極座標)変調の2種類に大別されます。今回の研究では、大出力電力化に有利なポーラ変調を基盤とした新しい送信機アーキテクチャを提案しました。

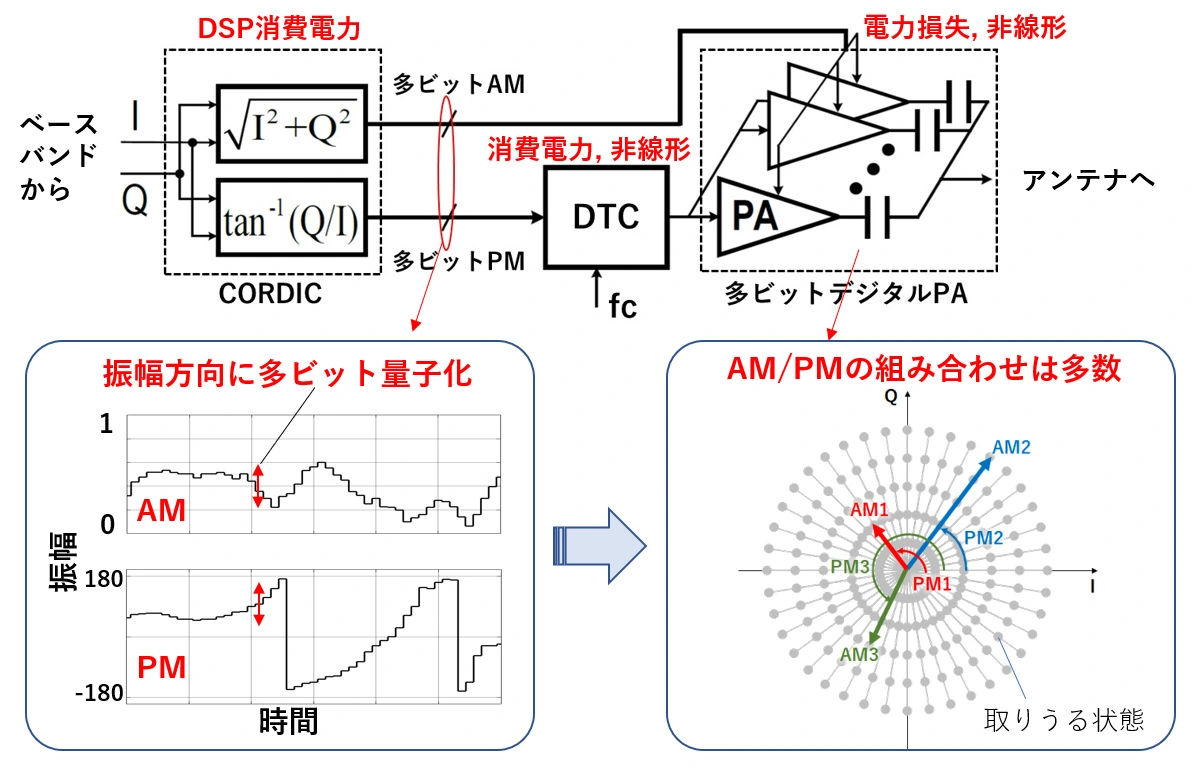

従来のデジタルポーラ変調送信機の構成では、ベースバンド出力のI(同相)およびQ(直交)信号を、CORDICを用いてポーラ変調用のAM(振幅)信号およびPM(位相)信号に変換しています(図2)。多ビットPM信号はデジタル時間変換器[用語8](DTC)を制御し、位相変調信号を生成して複数のデジタルPAに入力します。一方、多ビットAM信号は各PAのオン/オフを制御し、出力キャパシタに充電される電荷量を変えることで振幅変調を実現します。この構成では、CORDICによるデジタル信号処理、高線形かつ高速なDTC、さらに多ビットAMおよびPM信号の組み合わせによる複雑なスイッチング動作が必要となります。そのため、これらの処理がシステム全体の電力効率や線形性を低下させる点が課題とされていました。

図2.従来のデジタルポーラ変調送信機の構成と課題

研究成果

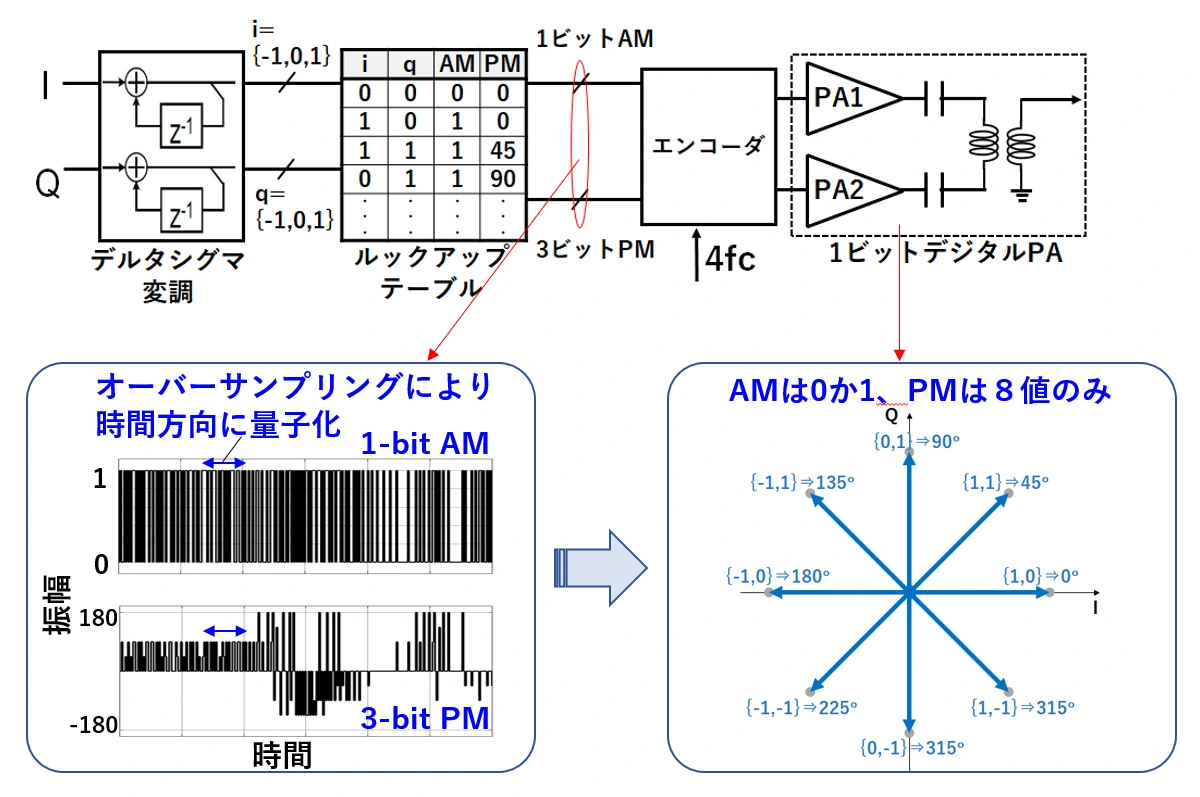

今回の研究では、従来のデジタルポーラ変調送信機の課題を解決するために、CORDICを用いないデジタルポーラ変調送信機を提案しました(図3)。この構成では、ベースバンドからのI信号とQ信号をオーバーサンプリングし、デルタシグマ変調[用語9]を用いて、それぞれを{-1, 0, 1}の3値に変換します。この結果、IとQの組み合わせを9つの状態としてルックアップテーブル(LUT)に格納できます。さらに、AM信号を3値から2値に切り捨てることにより、8つ(3ビット)の位相値と2つの振幅値(1ビット)からなるポーラ変調信号を、CORDICを使用せずにLUTを参照するだけで生成できます。取りうるAMとPMの状態数は減少しますが、時間軸方向のオーバーサンプリングにより、元の情報が失われることや信号対雑音比(SNR)が劣化することはありません。

図3.今回提案したCORDICを用いないデジタルポーラ変調送信機の構成

この構成では、AM信号は、3値から2値に切り捨てる際に発生する誤差を補正します。一方でPM信号は、位相状態が180°以上変化した際に発生するオーバーラップを補正する処理を行った後、1ビット信号にコーディングされデジタルPAに入力されます。デジタルPAは、出力電力を増大させるために2つのPAをトランスで電力合成しています。この時、出力電力が小さい領域では、2つのPAに入力する信号間に1サイクル分の遅延を導入しています(インターリーブ)。この手法により、負荷変調効果が生じるため、小出力電力時の電力効率が向上します。

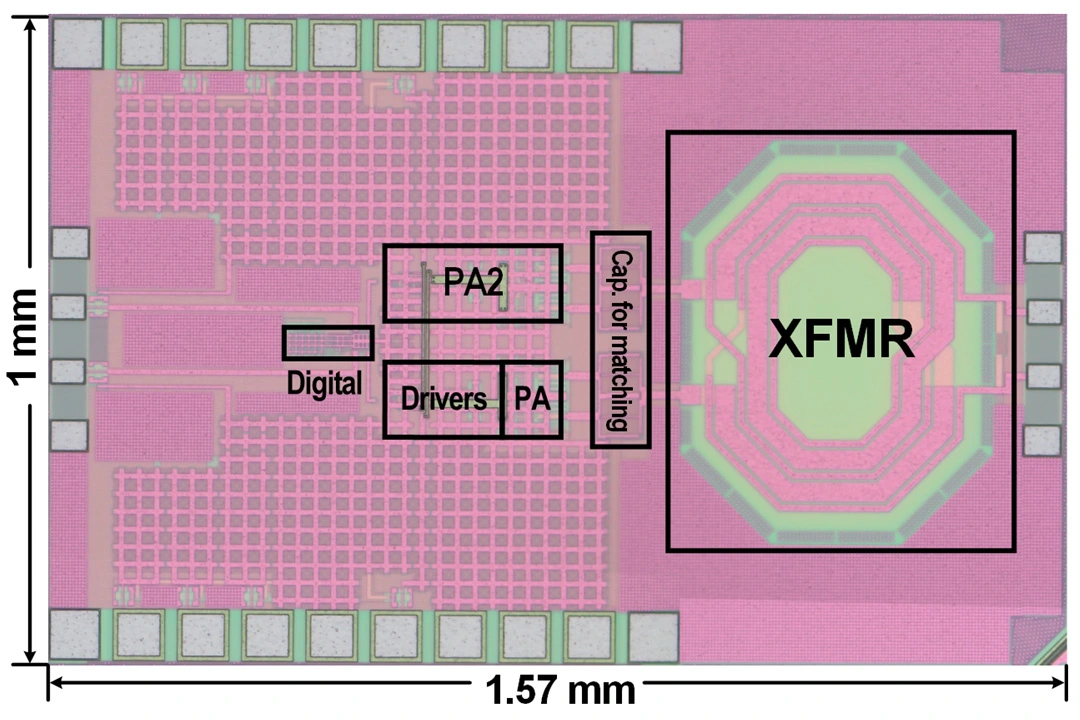

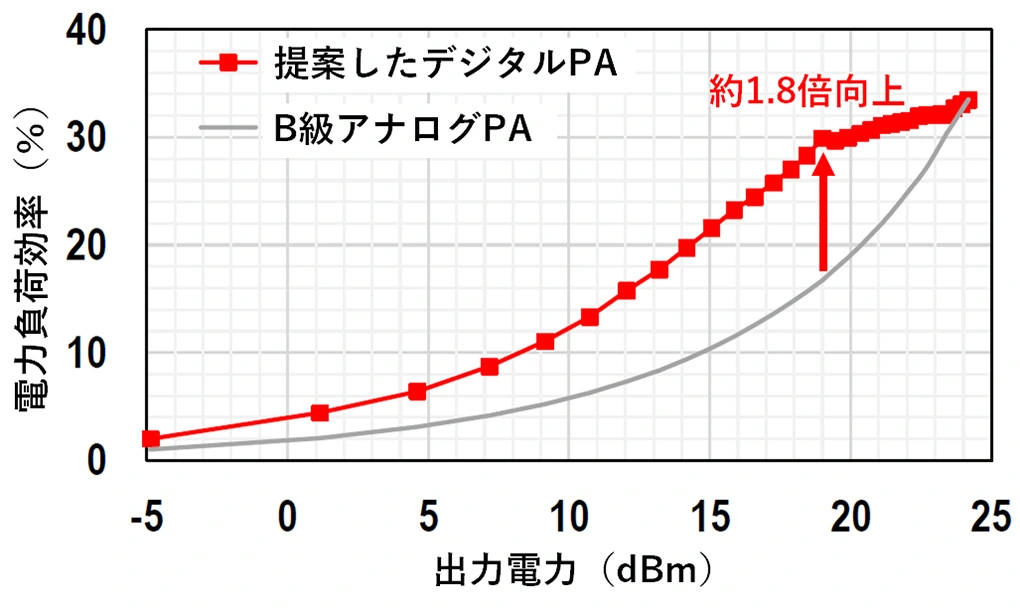

提案したデジタルポーラ変調送信機を、65 nm CMOSプロセスを用いて1 mm x 1.57 mmのチップサイズで作製しました(図4)。開発した送信機CMOS ICは、周波数1.35 GHzの連続波信号に対して、出力電力24.2 dBm、最大電力負荷効率33.5%を達成し、CMOS PAとして優れた特性を実証しました。特に低出力領域の効率は、インターリーブ技術を採用したことにより、B級アナログPAに比べて約1.8倍向上しています(図5(a))。

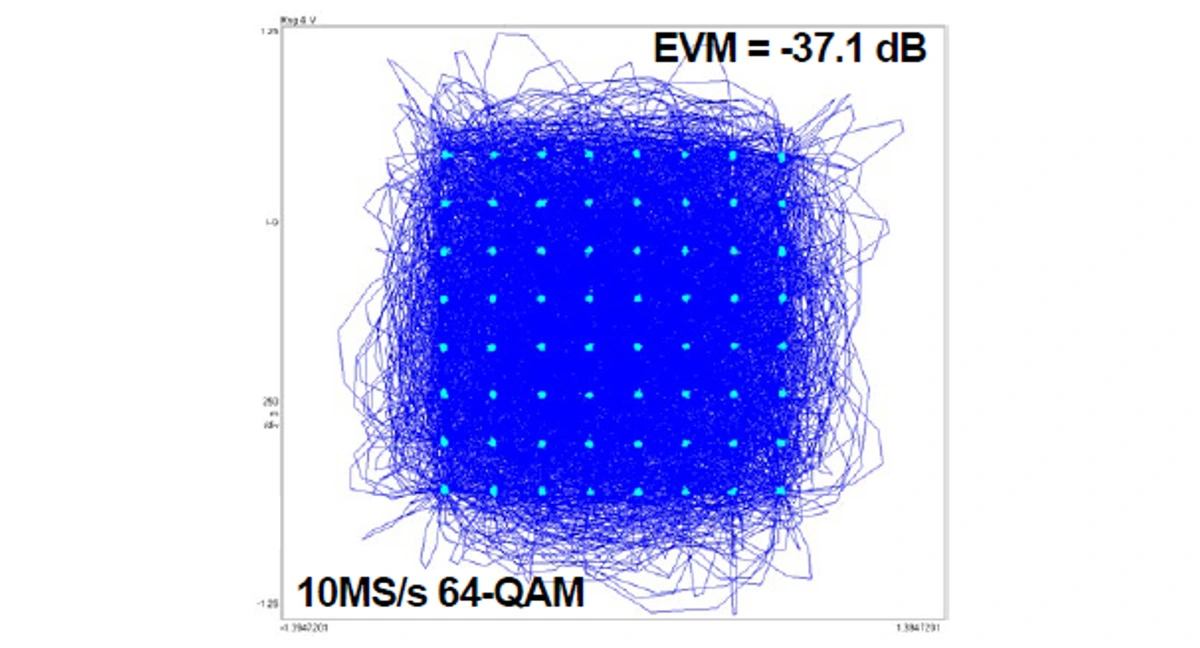

また、変調信号による評価を行ったところ、エラーベクトル強度(EVM)は、64QAMでシンボルレート10 MS/s時には-37.1 dB(図5(b))、256QAMで50 MS/s時には-28.7 dBとなり、外部のデジタル歪補償技術[用語10]を用いることなく、システム要求を満足することが確認できました。さらに電力負荷効率は、いずれの条件においても20%を超えており、提案したデジタルポーラ変調送信機が、高い電力効率と線形性を両立する優れた方式であることを実証しました。

図4.作製したデジタルポーラ変調送信機CMOS ICのチップ写真

(a)電力負荷効率

(b)EVM

- 図5.作製したデジタルポーラ変調送信機CMOS ICの特性

社会的インパクト

本研究では、デジタル回路向けの微細CMOSプロセスとの親和性が高く、小型・低消費電力にSoC集積可能なデジタル送信機で、高電力効率と高線形特性を実現しました。この送信機ICは、CORDICを用いないアーキテクチャを採用しているため、既存のベースバンドとの接続が容易です。さらにデジタルリッチな構成であるため、設計の柔軟性が高く、異なる通信規格や周波数の変更も容易で、いわゆるソフトウェア無線[用語11]への適用も期待できます。これらにより、IoT機器の小型・低消費電力化や低コスト化が可能となり、Beyond 5GにおけるIoTサービスの普及に貢献できます。

今後の展開

今後は今回の研究成果をさらに発展させて、さらなる高性能なデジタル送信機を実現するアーキテクチャや回路方式を探求するとともに、IoTデバイスなどの実際のアプリケーションでの効果も実証していきます。

- 付記

本研究は、国立研究開発法人情報通信研究機構(NICT(エヌアイシーティー))の委託研究「継続的進化を可能とするB5G IoT SoC及びIoTソリューション構築プラットホームの研究開発」(JPJ012368C00801)の成果の一部である。

- 用語説明

| [用語1] | アナログPA:入力アナログ信号を、忠実に同じ波形のまま、線形に増幅して送信する電力増幅器。動作級により、A級、B級、C級などに分類され、A級は線形性は高いが効率が低く、C級は効率は高いが線形性が低いなど、効率と線形性の間にトレードオフが存在する。 |

|---|---|

| [用語2] | デジタルPA:入力信号をデジタル信号に変換し、デジタル波形にしたものを増幅し、フィルタ等でアナログ波形に戻して送信する電力増幅器。スイッチングアンプ、D級アンプとも呼ぶ。 |

| [用語3] | ポーラ変調:信号をAM(振幅)成分とPM(位相)成分に分解し、それぞれ独立に処理して、電力増幅器で合成、信号再生する方式。 |

| [用語4] | CORDIC(コーディック):(COordinate Rotation DIgital Computerの略)三角関数や対数、平方根などの関数演算をハードウェアで実行するアルゴリズム。加算、減算、ビットシフトの繰り返しで演算を行うため、一般にはハードウェア実装が容易であるが、高精度化には課題がある。 |

| [用語5] | CMOSプロセス:N型とP型のMOSFETを相補的に用いた集積回路で、バイポーラプロセスと比較して消費電力の削減と高い集積率を実現したプロセス。近年の集積回路はほぼ全てがCMOSプロセスとなっている。 |

| [用語6] | SoC(システム・オン・チップ):1つのチップ上に、システムを構成する複数の機能を集積した半導体集積回路。無線通信用SoCでは、RF回路やベースバンド回路、電源管理回路、記憶回路、インターフェースなどが集積されている。 |

| [用語7] | 直交変調:信号を直交するI(同相)成分とQ(直交)成分に分解し、それぞれ独立に処理、電力増幅器で増幅した後に合成する方式。 |

| [用語8] | デジタル時間変換器(DTC):( Digital-to-Time Converterの略)デジタル制御値により、遅延時間が変化する可変遅延回路。 | [用語9] | デルタシグマ変調(DSM):(Delta-Sigma Modulationの略)信号の大きさをパルスの密度で表現するパルス密度変調の一種。信号帯域よりも十分高いサンプリング周波数により標本化(オーバーサンプリング)を行い、帰還回路によって量子化雑音の分布を制御できる(ノイズシェーピング)のが特徴。 |

| [用語10] | デジタル歪補償(DPD):(Digital Predistortionの略)信号の非線形性を補償するための技術。対象となる増幅器や送信機の非線形性をモデル化し、その逆特性の信号を入力することで、線形の出力信号を得る技術。 |

| [用語11] | ソフトウェア無線(SDR):(Software-Defined Radioの略)無線通信システムの信号処理をハードウェアではなくソフトウェアで実現する技術。異なる通信規格に対応可能な柔軟で再構成可能なシステムが構築できる。 |

- 論文情報

| 学会: |

2025 IEEE International Solid-State Circuits Conference(ISSCC) プログラム |

|---|---|

| 講演セッション: | Session 5 – Front-End Circuits for High-Performance Transceivers |

| 講演時間: | 現地時間2月17日午後3時35分 |

| タイトル: |

A Power-Efficient CORDIC-less Digital Polar Transmitter Using 1b DSM-Based PA Supporting 256-QAM |

| 著者: |

Y. Zhang, Z. Liu, D. Li, M. Tang, Y. Zhang, H. Huang, D. Xu, W. Madany, A. A. Fadila, W. Wang, Y. Xiong, D. Zhang, G. P. Kusuma, H. Sakai, K. Kunihiro, A. Shirane, K. Okada |

研究者プロフィール

岡田 健一 Kenichi OKADA

東京科学大学 工学院 電気電子系 教授

研究分野:無線機・高周波回路(RF回路、ミクストシグナル回路)

張 雲程 Yuncheng ZHANG

東京科学大学 工学院 電気電子系 助教

研究分野:無線機・高周波回路(RF回路、ミクストシグナル回路)

関連リンク

- 6Gに向けた高効率・低消費電力のミリ波帯 MIMOフェーズドアレイ受信機を開発|旧・東京工業大学

- サブテラヘルツ帯CMOS ICで640 Gbpsの無線伝送に成功|旧・東京工業大学

- Beyond 5Gに向けた新規デジタル位相同期回路を開発|旧・東京工業大学

- オールCMOSの300 GHz帯フェーズドアレイ送信機を開発|旧・東京工業大学

- 300 GHz帯でのビームフォーミングと高速データ伝送に成功|旧・東京工業大学

- 6G向け100 Gbps超の超高速サブテラヘルツフェーズドアレイ無線機を開発|旧・東京工業大学

- 低軌道衛星コンステレーションに向けた耐放射線Ka帯フェーズドアレイ無線機の開発に成功|旧・東京工業大学

- 小型地球観測衛星搭載用のKa帯フェーズドアレイ無線機の低消費電力化に成功|旧・東京工業大学

- 新アーキテクチャのデジタル位相同期回路を開発|旧・東京工業大学

- Beyond 5Gの端末機に向けたマルチバンドフェーズドアレイ受信ICを開発|旧・東京工業大学

- 超小型衛星搭載用Ka帯無線機の開発に成功|旧・東京工業大学

- 5GおよびBeyond 5Gの基地局に向けた高効率ミリ波帯フェーズドアレイ無線機を開発|旧・東京工業大学

- 超高速ビームフォーミングが可能なミリ波帯フェーズドアレイ無線機を開発|旧・東京工業大学

- 東工大の教職員3人に2023年IEEEフェローの称号を授与|旧・東京工業大学

- 「異分野融合研究支援」を創設 3チームに授与|旧・東京工業大学

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ — 岡田健一|旧・東京工楯大学

- 岡田健一 Kenichi Okada|研究者検索システム Science Tokyo STAR Search

- 張雲程 Yuncheng ZHANG|研究者検索システム Science Tokyo STAR Search

- 岡田研究室

- 電気電子コース(大学院課程)|教育|工学院 電気電子系

- 電気電子系(学士課程)|教育|工学院 電気電子系

- 工学院|大学組織一覧|Science Tokyoについて