電気電子系 News

新アーキテクチャのデジタル位相同期回路を開発

ジッタ特性を大幅に改善、IoT向け低消費電力Beyond 5Gデバイスの普及を加速

要点

- 新しい非均一オーバーサンプリング手法を用いたデジタル位相同期回路を開発。

- 雑音の大きいサンプリング領域を排除し、位相同期回路のジッタを大幅に低減。

- デジタル機器の小型化・低消費電力化を実現し、IoT向けLow-Power Beyond 5Gデバイスの普及を加速。

概要

東京工業大学 工学院 電気電子系の岡田健一教授(電気電子コース 主担当)らの研究グループは、PLLのオーバーサンプリング[用語1]を非均一に行う新しいアーキテクチャによる、低消費電力・低ジッタ[用語2]特性のデジタル位相同期回路(PLL)[用語3]の開発に成功した。

PLLはこれまで、無線機器用集積回路の小型・低消費電力化や低コスト化を実現してきたが、ループ帯域幅[用語4]が狭い点が問題だった。オーバーサンプリング手法を用いたPLLでは、ループ帯域幅を稼げる一方で、サンプリング時の雑音の影響でジッタが大きくなる課題があった。

今回の研究では、雑音の影響の大きい部分のサンプリングを避けて非均一なオーバーサンプリングを行うという新たな手法でこの問題を解決した。開発したPLLを、最小の配線半ピッチ(幅)65 nm(ナノメートル)のシリコンCMOSプロセス[用語5]で試作し、200 kHzのループ利得[用語6]を4.95 psの低ジッタで実現した。消費電力は3.8 mWである。このPLLは今後、小型・低コスト、低消費電力を重視するIoT向けLow-Power Beyond 5G[用語7]デバイス等への応用が期待される。

研究成果は、2月19日~23日に米国サンフランシスコで開催される「ISSCC 2023(国際固体素子回路会議)」で発表される。

背景

32 kHzの水晶振動子から直接高周波の基準信号を生成するデジタル位相同期回路(Phase-Locked Loop、PLL)は、高周波用の振動子を不要にできることから、無線機器用の集積回路の小型・低消費電力化、低コスト化に大きく貢献してきた。しかしながら、32 kHzという低い参照信号によるPLLにはループ帯域幅が小さいという課題があった。この課題を解決するために、オーバーサンプリングの手法によってループ帯域幅を向上する提案がなされたが、従来の均一なオーバーサンプリングでは、参照電圧信号の雑音によってジッタが発生することが問題となっていた。

ジッタは、高周波デジタル信号を使用する最新の電子機器に共通する大きな問題であり、特にIoTに向けた無線機器には小型・低消費電力の低ジッタPLLが強く求められていた。

研究成果

今回の研究で開発したPLLでは、従来のオーバーサンプリングの課題を解決するため、オーバーサンプリングの間隔を非均一にする新しいアーキテクチャを提案し、ジッタを大きく低減した。

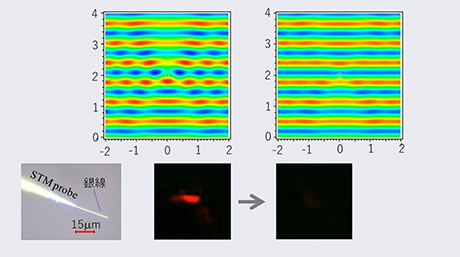

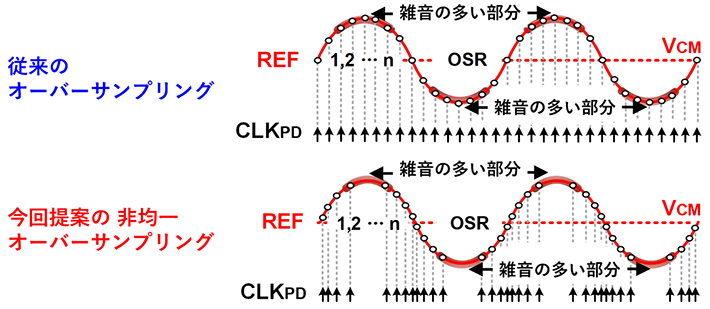

今回提案した非均一なオーバーサンプリング手法では、参照電圧信号のうち、雑音の多い部分は従来よりもサンプリングを減らし、他の部分を密にサンプリングする(図1)。これにより、位相検出器からのノイズの影響を低減し、PLLのジッタを大きく削減できる。

図1. 従来のオーバ-サンプリングと今回提案した非均一オーバーサンプリングの比較

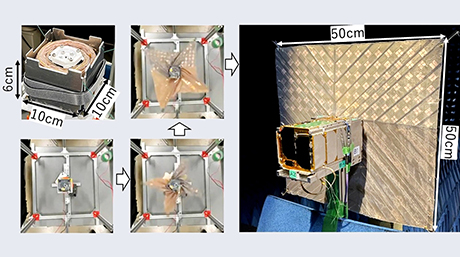

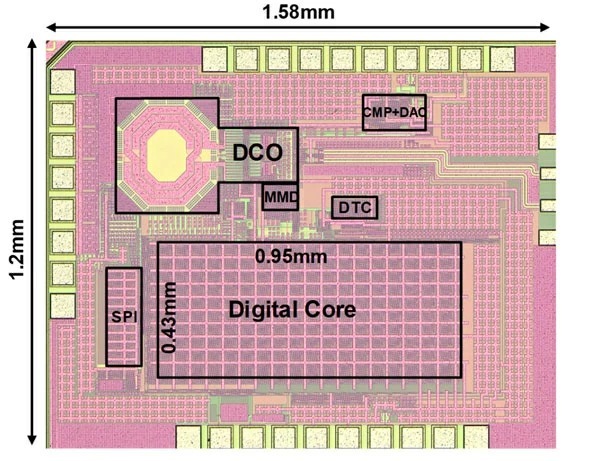

本アーキテクチャを用いたデジタルPLL回路を、65 nmのCMOSプロセスを用いて実際に作製した(図2)。チップサイズは1.58 mm x 1.2 mmで、新たに開発した利得増大位相検出器を内蔵し、異なるサンプリングポイントのループ利得を動的に調整できるようにした。

作製した回路を評価した結果、200 kHzのループ帯域幅を4.95 psの低ジッタで実現できていることがわかった。消費電力はわずか3.8 mWであった。

図2. 作製したPLL回路のチップ写真

社会的インパクト

本研究で開発されたPLLは、高いエネルギー効率を必要とするアプリケーションの実現に貢献するものである。特に、近い将来には機器の個数が1兆個にも及ぶと言われるIoT機器は、インターネット接続のために通信回路が不可欠であり、その通信回路の性能の鍵となるのがPLLである。今回の成果であるジッタの小さい小型・低消費電力、低コストのPLLは、次世代通信ネットワークの要となる低消費電力 Beyond 5Gデバイスにも応用でき、IoTデバイスの普及を一気に加速すると期待できる。

今後の展開

本研究成果により、低ジッタで高品質な信号を、高い電力効率で低コストに得ることが可能となり、IoT機器用の通信回路をはじめ、次世代センサーデバイス、パワーデバイス等の多くのアプリケーションがその恩恵を受けると考えられる。

- 付記

本研究は、国立研究開発法人情報通信研究機構(NICT(エヌアイシーティー))の委託研究「継続的進化を可能とするB5G IoT SoC及びIoTソリューション構築プラットホームの研究開発」(採択番号00801)の成果の一部である。

- 用語説明

[用語2] ジッタ : クロックの重要な特性の一つであり、クロック信号の立ち上がりまたは立ち下りタイミングが揺らぐ現象。本来のタイミングからのずれが統計的にどれぐらいの幅を持つかで評価する。ジッタが小さいほど、クロックの揺らぎが小さい状況を示す。クロックを生成している発振器の位相雑音特性に大きく依存し、位相雑音が低いほど、ジッタも小さくなる。

[用語3] 位相同期回路(PLL : Phase-Locked Loop) : 集積回路中では正確な周波数基準が作れないため、水晶発振器による基準周波数f refを用い、それをN逓倍して所望周波数N・f refの周波数の信号を得る。そのための回路を位相同期回路(PLL)という。PLLには、位相周波数比較器、チャージポンプ、ローパスフィルタを用いるアナログPLLと、時間差デジタル変換器(TDC)とデジタルローパスフィルタを用いるデジタルPLL(オールデジタルPLLとも呼ばれる)が知られている。

[用語4] ループ帯域幅 : PLLの構成要素であるループフィルターのカットオフ周波数までの周波数帯域。ループ帯域幅が広いほど出力信号のレスポンスが向上する。

[用語5] CMOSプロセス : N型とP型のMOSFETを相補的に用いた集積回路であり、バイポーラプロセスと比較して消費電力の削減と高い集積率を実現したプロセスである。近年の集積回路はほぼすべてがCMOSプロセスとなっている。

[用語6] ループ利得 : PLLの負帰還ループを一巡した利得。ループ利得が1になる周波数までがループ帯域幅となる。

[用語7] Beyond 5G : 第5世代移動通信システム(5G)の次の世代の移動通信システム。

- 発表予定

この成果は2月19日~23日にサンフランシスコで開催される「2023 IEEE International Solid-State Circuits Conference (ISSCC 2023) : 2023年米国電気電子学会 国際固体素子回路会議」における講演セッション「Session 4 – A 32kHz-Reference 2.4GHz Fractional-N Nonuniform Oversampling PLL with Gain-Boosted PD and Loop-Gain Calibration」の講演タイトルで、現地時間2月20日午後3時15分から発表する。

- 講演情報

| 講演セッション : | Session 4 –Frequency Synthesizers |

| 講演時間 : | 現地時間2月20日午後3時15分 |

| 講演タイトル : | A 32kHz-Reference 2.4GHz Fractional-N Nonuniform Oversampling PLL with Gain-Boosted PD and Loop-Gain Calibration |

- ISSCC会議情報

- 低軌道衛星コンステレーションに向けた耐放射線Ka帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 小型地球観測衛星搭載用のKa帯フェーズドアレイ無線機の低消費電力化に成功|東工大ニュース

- Beyond 5Gの端末機に向けたマルチバンドフェーズドアレイ受信ICを開発|東工大ニュース

- 超小型衛星搭載用Ka帯無線機の開発に成功|東工大ニュース

- 無線電力伝送と無線通信双方に同時対応するミリ波帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 5GおよびBeyond 5Gの基地局に向けた高効率ミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- Beyond 5G向けIoTソリューション構築プラットフォームの研究開発を本格化|東工大ニュース

- 超高速ビームフォーミングが可能なミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 電源不要のミリ波帯5G無線機の開発に成功|東工大ニュース

- テラヘルツ帯でのフェーズドアレイ無線機を実現|東工大ニュース

- JAXAの「革新的衛星技術実証3号機」に5G対応のフェーズドアレー無線機を搭載|東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ — 岡田健一|研究ストーリー|研究

- 岡田健一教授が第18回ドコモ・モバイル・サイエンス賞を受賞|東工大ニュース

- 本学名誉教授ら4名が電子情報通信学会の2018年度業績賞などを受賞|東工大ニュース

- 「異分野融合研究支援」を創設 3チームに授与|東工大ニュース

- 岡田研究室

- 岡田健一 Kenichi Okada|研究者検索システム 東京工業大学STARサーチ

- 電気電子コース(大学院課程)|教育|工学院 電気電子系

- 電気電子系(学士課程)|教育|工学院 電気電子系

- 研究成果一覧