電気電子系 News

トポロジカル絶縁体による磁性体の超高速磁化反転に成功

超高速スピン軌道トルク磁気抵抗メモリの実用化へ加速

概要

電子材料・物性グループのファム・ナムハイ准教授(電気電子コース 主担当)、外国人特別研究員のNguyen Huynh Duy Khang(ゲィン・フン・ユィ・カン)研究員(研究当時)、NHK放送技術研究所の宮本泰敬主任研究員を中心とした共同研究チームは、トポロジカル絶縁体を用いて、垂直磁気異方性を持つ磁性薄膜を低電流密度かつナノ秒レベルの超高速に磁化反転させることに成功した。

本研究成果は、米国の学術誌「Applied Physics Letters」のEditor’s Pickとして掲載された。

背景

近年、スピン軌道トルク方式を利用した磁気抵抗メモリ(SOT-MRAM)は、超高速で動作可能であることから注目を集めている。SOT-MRAMでは、スピンホール効果を利用して電流からスピン流を生成し、このスピン流の作用によってデータの書き込み(磁化反転)を行う。その開発初期からスピン流源の材料として用いられている重金属は、スピンホール効果によるスピン流の生成効率を表すスピンホール角θSHが0.1台と小さい。そのため、垂直磁気異方性を持つ磁性薄膜を超高速磁化反転させるのに必要な電流密度が約3×108 A/cm2と極めて高く、実用上の問題があった。一方、近年注目されているトポロジカル絶縁体は、1を超える巨大なθSHを有するため、超高速磁化反転に必要な電流密度を劇的に低減することができると期待されている。

研究成果

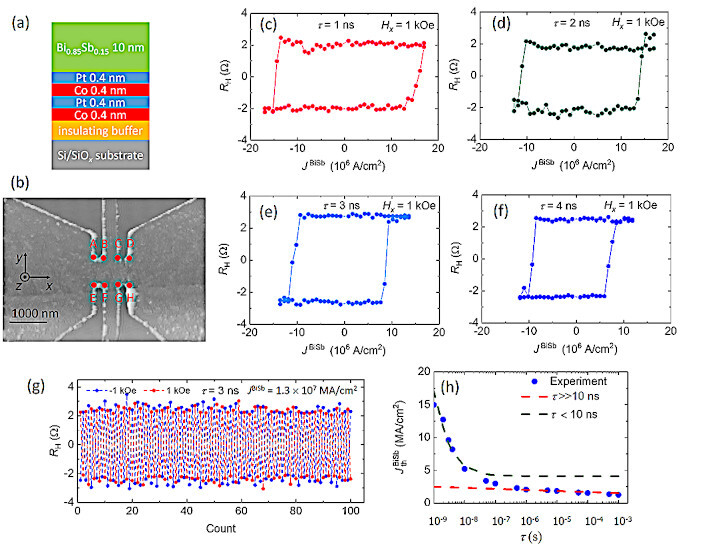

研究チームは、高い電気伝導率と巨大なスピンホール効果を有するBiSbトポロジカル絶縁体に注目してきた。今回の研究では、超高速磁化反転を実証するために、垂直磁気異方性の大きな(Pt/Co)多層膜とBiSbトポロジカル絶縁体との接合を、スパッタリング法を用いて酸化Si基板上に製膜した(図1(a))。次に、1,000 nm × 800 nmの素子を作製し(図1(b))、パルス幅が1~4ナノ秒のパルス電流を掃引した時の磁化反転を評価した(図1(c)~(f))。また、3ナノ秒の正負のパルス電流(1.3×107 A/cm2)をBiSbに連続的に印加した時の磁化反転も評価した(図1(g))。面内に印加したバイアス磁場の向きを逆にすると、磁化反転の向きが逆になったことから、SOT方式による超高速磁化反転が確認された。

さらに研究チームは、磁化反転に必要な電流密度の大小の指標として、絶対零度における閾値電流密度Jthoを評価した。今回作製した素子に1ナノ秒から1ミリ秒までの様々なパルス電流を印加し、磁化反転に必要な閾値電流密度を測定した(図1(h))。電流のパルス幅が100ナノ秒より長い場合、磁化は熱揺らぎによるアシストを受けるため、Jthoよりも小さい電流密度で反転する。熱揺らぎによるアシストの領域の電流密度を外挿すると、Jtho=2.5×106 A/cm2が得られた(図1(h)の赤の点線)。一方、パルス幅が10ナノ秒よりも短い場合には、必要な電流密度はパルス幅と逆比例して急増し、Jthoよりも高くなる。この超高速領域を外挿すると、Jtho=4.1×106 A/cm2が得られた(図1(h)の緑の点線)。いずれのJthoの値も、従来研究されてきた重金属のJthoより2桁小さい。これらの結果により、トポロジカル絶縁体を用いることによって、超高速磁化反転に必要な電流密度を劇的に低減することに成功した。

- 図1(a)超高速磁化反転を実証するための膜構造。(b)作製した素子の写真。(c)-(f)パルス幅 1~4ナノ秒のパルスナノ秒電流を掃引した時の磁化反転。(g)3ナノ秒の正負のパルス電流(1.3×107A/cm2)をBiSbに連続的に印加した時の磁化反転。(h)1ナノ秒から1ミリ秒まで、様々なパルス電流を印加した時の磁化反転に必要な閾値電流密度。

今後の展開

今回作製した素子では、サイズが約1,000 nm × 800 nmと比較的大きいにもかかわらず、低電流密度で1~4ナノ秒の磁化反転を実現できたことから、素子サイズを90 nm以下に微細加工すれば、低電流密度で200ピコ秒の超高速磁化反転が期待できる。このスピードは、現在使われている最速の半導体メモリSRAMと並ぶ。したがって本研究成果は、将来的に半導体電子回路のキャッシュメモリを不揮発化させることで、ICT機器の低消費電力化に貢献するものだといえる。

- 論文情報

| 掲載誌: | Applied Physics Letters |

|---|---|

| 論文タイトル: | Nanosecond ultralow power spin orbit torque magnetization switching driven by BiSb topological insulator |

| 著者: | Nguyen Huynh Duy Khang, Takanori Shirokura, Tuo Fan, Mao Takahashi, Naoki Nakatani, Daisuke Kato, Yasuyoshi Miyamoto, and Pham Nam Hai |

| DOI: |

10.1063/5.0084927 |

- 高スピン流生成効率と高熱耐久性を両立する新材料の開発に成功|東工大ニュース

- トポロジカル絶縁体と磁気トンネル接合を集積した次世代不揮発性メモリSOT-MRAMの実証に成功|東工大ニュース

- 巨大な一方向性スピンホール磁気抵抗効果を実証|東工大ニュース

- トポロジカル絶縁体で世界最高性能の純スピン注入源を開発|東工大ニュース

- スピン自由度を用いた次世代半導体デバイス実現へ大きな進展|東工大ニュース

- 半導体のパラダイムシフトを起こす「スピントロニクス」に賭ける — ファム・ナム・ハイ|研究ストーリー|研究

- Pham准教授が日本磁気学会の優秀研究賞を受賞|電気電子系News

- ファム・ナム・ハイ准教授がドイツ・イノベーション・アワード「ゴットフリード・ワグネル賞2019」を受賞|東工大ニュース

- PHAM NAM HAI RESEARCH GROUP

- ファム研究室 ―研究室紹介 #30―|電気電子系News

- すばらしい研究者の紹介 #4 -ファム ナム ハイ准教授-|電気電子系News

- 研究者詳細情報(STAR Search)- PHAM NAM HAI(ファム ナム ハイ)

- 電気電子系(学士課程)|教育|工学院 - 電気電子系

- 電気電子コース(大学院課程)|教育|工学院 - 電気電子系

お問い合わせ先

東京工業大学 工学院 電気電子系

准教授 ファム・ナム・ハイ

E-mail : pham.n.ab@m.titech.ac.jp

Tel : 03-5734-3934 / Fax : 03-5734-3870