電気電子系 News

世界最小のクロック回路を5 nm CMOSで開発

要点

- 世界初5 nm CMOSプロセスを用いた分数分周型クロック回路を実現

- 世界最小・最高性能のスペクトル拡散クロック回路の開発に成功

- デジタル回路のみで構成でき、自動合成による超短期間設計が可能

概要

東京工業大学 工学院 電気電子系の岡田健一教授らと株式会社ソシオネクストの研究グループは、最先端の5 nm FinFET CMOSプロセス[用語1]で世界初となる世界最小の高性能分数分周型クロック回路[用語2]の開発に成功した。この回路はプロセッサーやメモリー、通信用のクロック用途として必須の電子回路であり、開発したクロック回路は小型ながらも優れたジッタ特性[用語3]を持つ。また、細かい周波数調整が可能な分数分周型PLL[用語5]で構成されており、スペクトル拡散クロック[用語6]の生成が可能である。

一般にクロック回路は典型的なアナログ回路であり、従来はアナログ回路設計者が時間をかけて設計・チューニングする必要があったが、本技術ではクロック回路をデジタル回路として構成することを可能とした。通常のデジタル回路と同様に自動配置配線が可能となり、非常に短時間で必要なプロセスやクロック周波数に合わせて最適に設計することができる。また、製造プロセスの微細化にあわせてスケーラブルに回路面積を小型化することが可能であり、幅広い用途のSoC[用語7]の小型化・低コスト化を実現できる。

研究の背景・意義

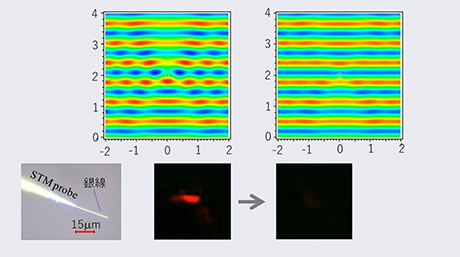

携帯電話、パソコン、テレビなどを含むほとんどの電子機器に搭載されているLSI(大規模集積回路)は、デジタル信号処理を行うデジタル回路部と、外部からのアナログ信号を扱うアナログ回路部から構成される。LSIを製造する半導体製造プロセスの微細化にあわせてデジタル回路は小型化・高性能化が可能であるが、アナログ回路は小型化が困難であり、また、微細な製造プロセスほど設計が困難になることが大きな問題となっている(図1)。

図1. 半導体プロセスのスケーリング(左)とPLL回路設計の難易度(右)

LSIには、所望の周波数のクロック信号や通信用搬送波信号を生成するクロック回路が搭載されている。LSIに内蔵されるクロック回路は通常PLL方式のクロック回路が用いられる。PLLは典型的なアナログ回路の一種であり、FinFETのような最先端の半導体製造プロセスを用いる場合に、従来に比べて、設計がより困難となり、また、デジタル回路部分に比べて相対的に回路面積が大きくなる問題がある。

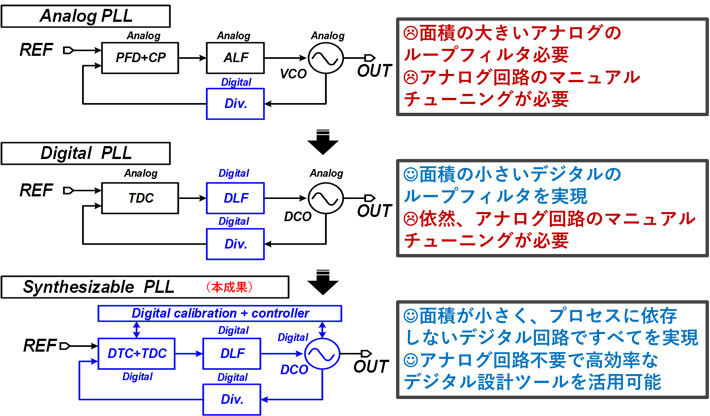

一般にアナログ型のPLLは優れたジッタ特性を持つことができる一方で、キャパシターやインダクターなどの回路面積の大きいアナログ素子を用いることになり、特に20 nm以下の先端プロセスでは微細プロセスの利点を失わせかねない課題を抱えている。また、通常アナログ回路は手作業で設計・レイアウトが行われるが、先端プロセスではアナログ回路の設計ルールが複雑化し、設計・検証の反復のコストが増大してしまう問題がある(図1)。さらに、高周波回路は回路寸法が大きくなればなるほど意図しない抵抗や容量による寄生成分が増え、アナログ素子による面積増大が性能劣化につながる。また、従来からデジタル型のPLLについて検討は行われていたが(図2)、回路ブロックの一部にアナログ回路が含まれており、依然としてアナログ回路の手設計が必要であった。本提案技術であるシンセサイザブルPLLでは、構成する回路ブロックをすべてデジタル回路構成とすることができ、あたかもデジタル回路のように自動設計を可能とすることに成功した(図2)。これにより、半導体製造プロセスの微細化にあわせて回路面積の縮小が可能となり、低消費電力化が期待できる。従来方式と比較すると、最先端の微細なプロセスを使うほどに性能の向上が期待できる。

図2. PLL回路の発展

PLLには生成できる周波数が基準信号に対して整数倍の周波数のみか、あるいは非整数倍(分数倍)の周波数を出力可能かで、それぞれ整数分周型(インテジャーN型)PLLと分数分周型(フラクショナルN型)PLLの二つの種類がある。無線機やSoCなどでは、任意の周波数の発生が可能な分数分周型PLLが必要である。分数分周型PLLは汎用性が高く、様々な用途での利用が可能であるが、一方で設計の難易度が高いことが問題であった。

研究成果

今回の成果は、従来のデジタルPLLにおいて、アナログ回路構成で実現されていたデジタル制御発振器(DCO)[用語8]および時間差デジタル変換器(TDC)[用語9]をデジタル回路構成により実現できたことによる(図2)。従来のデジタルPLLでは、TDC回路で長い時間差の変換が必要であったため、アナログ回路設計による高線形なTDCが必要であった。本研究成果では、タイミングをデジタル的に制御するデジタル時間変換器(DTC)[用語10]とTDC回路とを組み合わせることで、TDC回路に必要な時間差範囲を狭めることに成功し、そのデジタル回路化に成功した。一方で、DTC回路には長い時間差での変換が必要になるが、デジタル補正を組み合わせることでこの問題を解決した。DCO回路においても、同様にデジタル補正を駆使することでデジタル回路化を実現した。以上により、PLL回路全体をデジタル回路として構成することが可能となり、デジタル回路開発で使用されている回路合成・タイミング設計や自動配置配線ツールを活用できるようになり、通常のデジタル回路同様に、PLLをスタンダードセルによって自動設計できるようになった。これは異なるプロセス間での移植性を高め、新たに開発された最先端製造プロセスにおいても迅速な回路設計を可能とする。

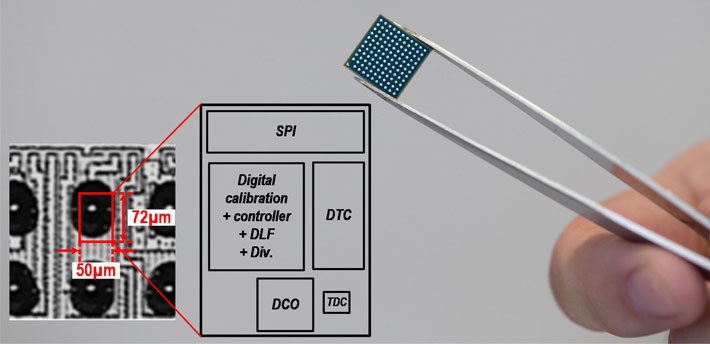

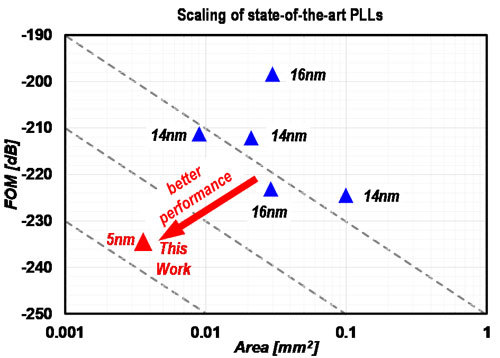

図3は作製したチップ写真である。実現した回路は、分数分周型(フラクショナルN型)のPLLで、わずかな面積で高周波信号の生成が可能なリングオシレータ[用語11]型の発振器を用いた。回路面積は世界最小の0.0036mm2であり(図4)、消費電力とジッタ特性に関する性能指標であるFoM[用語12]が-235 dB(デシベル)と、極めて優れた性能を達成した(表1)。わずか0.95mWの消費電力で動作し、スプリアスレベル[用語13]は低く-44 dBcであった。さらにスペクトル拡散クロック機能を有し、低電磁妨害特性を実現した。

本研究成果は、1月27日に集積回路設計技術において権威のあるジャーナルのひとつである「IEEE Solid-State Circuit Letters(米国電気電子学会 固体素子回路レター誌)」に掲載された。

なお本研究は株式会社テラピクセル・テクノロジーズの協力により実現した。

図3. 提案回路を搭載したチップ写真

表1 20 nmノード以降の先端CMOSプロセスにおけるPLL性能比較

| 本研究 | TCAS-I’18 | RFIC’18 | ISSCC’15 | ISSCC’15 | |

|---|---|---|---|---|---|

| 発表組織 | 東工大 & ソシオネクスト |

インテル | サムスン | TSMC | サムスン |

| 自動合成可能か? (Synthesizable) |

Yes | No | No | No | No |

| 製造CMOS プロセスノード |

5 nm | 14 nm | 14 nm | 16 nm | 14 nm |

| 面積 [mm2] | 0.0036 | 0.021 | 0.1 | 0.029 | 0.009 |

| 消費電力[mW] | 0.95 | 2.6 | 36.3 | 3.9 | 2.06 |

| ジッタ[ps] | 1.90 | 15.1 | 0.982 | 3.48 | 18.8 |

| 性能指標FOM*[dB] | -235 | -212 | -225 | -223 | -211 |

![]()

図4. 20 nmノード以降の先端CMOSプロセスにおけるPLL回路面積およびFOM比較

今後の展開

本提案技術である高性能クロック回路により、世界最先端の5 nmプロセスによる高性能、低消費電力、小面積のSoCを短期間で設計することが可能になった。また、クロック回路のデジタル化により、将来のSoCの全自動設計への道が拓かれた。ソシオネクストは今回の成果をもとにAIやIoTなど今後も継続して市場の成長が予想される分野で商品やサービスの差異化に寄与するSoCを供給していく。また東工大とソシオネクストは今後も、アナログデジタル変換器などの他の種類のアナログ回路の自動合成を始めとするCMOSミックストシグナル設計の基礎技術開発の分野で協力していく。

- 用語説明

[用語1] 5 nm FinFET CMOSプロセス : CMOSプロセスはN型とP型のMOSFET(金属酸化膜半導体電界効果トランジスタ)を相補的に用いた集積回路であり、バイポーラプロセスと比較し消費電力の削減と高い集積率を実現したプロセスである。近年の集積回路はほぼCMOSプロセスとなっている。nm(ナノメートル)は10億分の1 m。Finはシリコン基板を短冊状に成形した魚の背びれ状の構造。

[用語2] 分数分周型クロック回路 : 分数分周型(フラクショナルN型)PLL

PLL[用語5]にはインテジャーN型(整数分周型)とフラクショナルN型(分数分周型)がある。インテジャーN型PLLでは基準信号に対して整数倍の周波数を出力するが、フラクショナルN型では分数倍の任意の周波数の出力が可能である。例えば、水晶発振器から入力される基準クロック周波数が26 MHzの場合、インテジャーN 型PLLでは2,418 MHz(93倍)、2,444 MHz(94倍)、2,470 MHz(95倍)の生成が可能であるが、フラクショナルN型PLLでは2,442 MHz(93.923倍)のような任意の小数精度の逓倍動作が可能である。BLE等の無線通信用には、インテジャー型ではなくフラクショナル型のPLLが必要である。アナログPLLではフラクショナル型を比較的容易に実現できるが、小面積低消費電力で有利なデジタルPLLにおいてフラクショナル型のものはジッタ特性が劣化しやすく実現が難しい。

[用語3] ジッタ特性 : クロックの重要な特性の一つで、クロック信号の立ち上がりまたは立ち下りタイミングが揺らぐ現象で、本来のタイミングからのずれが統計的にどれぐらいの幅を持つかで評価する。ジッタが小さいほど、クロックの揺らぎが小さい状況を示す。クロックを生成している発振器の位相雑音[用語4]特性に大きく依存し、位相雑音が低いほど、ジッタも小さくなる。

[用語4] 位相雑音 : 発振器の重要な特性の一つ。必要な周波数の信号に対し、どれだけ不要な周波数のスペクトルを持つかを表す。一般に、位相雑音特性は電力や発振周波数帯に依存する。

[用語5] PLL(Phase-Locked Loop) : 集積回路中では正確な周波数基準が作れないため、水晶発振器による基準周波数frefを用い、それをN逓倍して所望周波数N・frefの周波数の信号を得る。PLLには、位相周波数比較器、チャージポンプ、ローパスフィルタを用いるアナログPLLと、時間差デジタル変換器(TDC)とデジタルローパスフィルタを用いるデジタルPLL(オールデジタルPLLとも呼ばれる)が知られている。

[用語6] スペクトル拡散クロック : デバイスのクロック信号によって生じる外部への電磁妨害を抑えるための技術。デジタル回路は通常クロック信号を基準に動作するため、それに同期したタイミングで配線に電流が流れ、特定のクロックの周波数に集中した電磁妨害を発生してしまう。電磁妨害の対策として金属のシールド等も用いられるが、物理的な実装が必要なためサイズやコストが増大してしまう。一方でスペクトル拡散クロックは、クロックの周波数を意図的に変化させることで、使用する周波数帯域を広げながらエネルギーを拡散させ、電気的に電磁妨害が発生しにくい状態を作り出すことができる。

[用語7] SoC(System on Chip) : プロセッサーやメモリー、その他システムを実現するために必要となるすべての回路が集積された集積回路。特に用途にあわせて設計したSoCをカスタムSoCと呼ぶ。

[用語8] デジタル制御発振器(DCO :Digitally Controlled Oscillator) : デジタル制御値により発振周波数が変化する発振回路。PLLの発振周波数とリファレンス周波数の偏差に応じてDCOに与えるデジタル制御値が決まり、偏差を低下させるようにDCOの発振周波数は変化する。PLLの出力周波数はDCOの発振周波数と一致する。

[用語9] 時間差デジタル変換器(TDC : Time-to-Digital Converter) : 二つの入力信号の時間差をデジタル値に変換して出力する回路。PLLなどの幅広い回路で利用されている。

[用語10] デジタル時間変換器(DTC : Digital-to-Time Converter) : デジタル制御値により、遅延時間が変化する可変遅延回路。デジタル制御遅延回路(DCDL, Digitally-Controlled Delay Line)とも呼ばれる。PLLなどの幅広い回路で利用されている。

[用語11] リングオシレータ : 遅延素子を環状に接続して構成する発振器。可変遅延機構を加えることで周波数を可変とし、デジタル制御発振器を構成することができる。

[用語12] FoM : Figure of Meritの略で、消費電力で規格化したジッタ性能を示す。ジッタと消費電力はトレードオフの関係にあり、発振器の消費電力を増やすとジッタが減少し、消費電力を減らすとジッタが増加する。FoMは、ジッタの標準偏差(σt)と消費電力PDCを用いて、以下の式で定義される。

![]()

ジッタ特性が同じでFoMが10dB小さければ、消費電力が10分の1であることに相当する。

[用語13] スプリアスレベル : スプリアスとは必要な信号以外の信号(ここではクロック周波数以外の不要な信号)のことであり、スプリアスレベルはこの不要な信号の強度を表す。スプリアスレベルが高いことは不要な信号が強いことを示し、その場合デジタル回路の誤動作や通信の品質低下、妨害波の発生に影響を与える。デシベル表現で示されることが多く、例えば-44 dBcは必要な信号の電力に対して不要な信号がおよそ25,000分の1に抑えられていることを表す。

- 論文情報

| 掲載誌 : | IEEE Solid-State Circuits Letters |

|---|---|

| 論文タイトル : | A Fully-Synthesizable Fractional-N Injection-Locked PLL for Digital Clocking with Triangle/Sawtooth Spread-Spectrum Modulation Capability in 5 nm CMOS |

| 著者 : | Bangan Liu(東工大 研究員)、Yuncheng Zhang(東工大 博士後期課程学生)、 Junjun Qiu(東工大 博士後期課程学生)、Hongye Huang(東工大 博士後期課程学生)、 Zheng Sun(東工大 博士後期課程学生)、Dingxin Xu(東工大 修士課程学生)、 Haosheng Zhang(東工大 博士後期課程学生)、Yun Wang(東工大 研究員)、Jian Pang(東工大 研究員)、Zheng Li(東工大 修士課程学生)、Xi Fu(東工大 修士課程学生)、白根篤史(東工大 助教)、黒須一司(ソシオネクスト)、中根美徳(ソシオネクスト)、正木俊一郎(ソシオネクスト)、岡田健一(東工大 教授) |

| DOI : | 10.1109/LSSC.2020.2967744 |

- 5G向けミリ波フェーズドアレイ無線機を開発│東工大ニュース

- 5G向けミリ波無線機の省面積化に成功│東工大ニュース

- 超省エネ・小型の原子時計の開発に成功│東工大ニュース

- 極低消費電力のデジタル位相同期回路を開発│東工大ニュース

- 世界最小電力で動作するBLE無線機を開発│東工大ニュース

- 5G向けミリ波無線機の小型化に成功│東工大ニュース

- 300 GHz帯で毎秒100ギガビットの無線伝送が可能な超高速ICを開発│東工大ニュース

- 水晶発振回路の高速起動化でIoT機器の消費電力を大幅低減│東工大ニュース

- 世界最高速!毎秒120ギガビットの無線伝送に成功│東工大ニュース

- 新型デジタル発振器を開発 ―電圧サブサンプリングにより低消費電力、低ジッタ実現―│東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ ― 岡田健一│研究ストーリー|研究

- 岡田健一教授が高柳健次郎業績賞を受賞|電気電子系 News

- 岡田健一教授が総務省 戦略的情報通信研究開発推進事業 研究開発奨励賞を受賞|電気電子系 News

- 東工大教員3名が平成29年度科学技術分野の文部科学大臣表彰で「科学技術賞」を受賞│東工大ニュース

- 松澤・岡田研究室―日経エレクトロニクスからNEアナログ・イノベーション・アワード優秀賞を受賞|電気電子系 News

- 松澤・岡田研究室 ―研究室紹介 #1―│電気電子系 News

- 岡田研究室

- 研究者詳細情報(STAR Search) - 岡田健一 Kenichi Okada

- 株式会社ソシオネクスト

- 研究成果一覧

お問い合わせ先

東京工業大学 工学院 電気電子系

教授 岡田健一

E-mail : okada@ee.e.titech.ac.jp

Tel : 03-5734-3764 / FAX : 03-5734-3764

株式会社ソシオネクスト

正木俊一郎

E-mail : masaki.shunichiro@socionext.com