電気電子系 News

世界最小電力で動作するBLE無線機を開発

デジタル化で実現、IoTの普及を加速

要点

- 新型デジタル発振器により大幅な低消費電力化を達成

- IoT機器への幅広い利用を期待

概要

東京工業大学 工学院 電気電子系の松澤昭教授と岡田健一准教授らの研究グループは、世界最小電力で動作するBluetooth Low Energy(BLE、ブルートゥース・ローエナジー)[用語1]無線機の開発に成功した。無線機の大部分をデジタル化することにより実現した。

BLE無線機は最小配線半ピッチ65 nm(ナノメートル) のシリコンCMOSプロセスで試作し、送信時2.9 mW(ミリワット)、受信時2.3 mWの極低消費電力で動作することを確認した。これは、これまでに報告されたBLE無線機の半分以下の消費電力である。長期間にわたり電池交換の必要がなくなり、IoT(Internet of Things、モノのインターネット)技術の普及を大きく加速させる成果である。

研究成果について、2月11日~15日に米国サンフランシスコで開かれる「ISSCC 2018(国際固体素子回路会議)」で2件の論文を発表する。

本研究開発の成果の一部は国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)委託事業「IoT推進のための横断技術開発プロジェクト」の結果得られたものである。

研究の背景・意義

消費電力の少ない無線技術は、IoT技術の適用範囲を広げる鍵となる技術として、近年盛んに研究開発が行われている。その中でも、BLEは、従来のBluetoothに比べて1桁以上の低消費電力化が可能であり、パソコン周辺機器やスマートフォンを中心に爆発的に利用が広がっている。メッシュネットワーク(端末同士が相互に通信を行う網の目状の通信ネットワーク)にも対応し、より幅広い種類のIoT端末への搭載が期待されている。

現状のBLE無線機はボタン電池1つで2~5年程度の駆動が可能だが、IoT端末の耐用年数中に電池交換を不要とするためには、10年以上の駆動が必要となり、BLE無線機にはさらなる低消費電力化が求められている。

研究成果

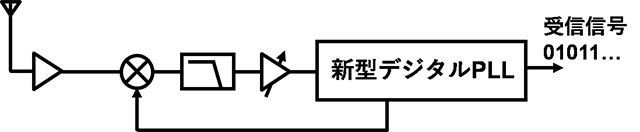

今回の研究成果は、大きく2つに分けることができる。1つは新型デジタル時間変換器(DTC : Digital-to-Time Converter)[用語2]により、低ジッタ[用語3]かつ広帯域な特性を実現した低消費電力デジタル位相同期ループ(PLL : Phase-Locked Loop)[用語4]で、もう1つは、そのデジタルPLL回路を用いて実現した世界最小電力で動作するBLE無線機に関するものである。

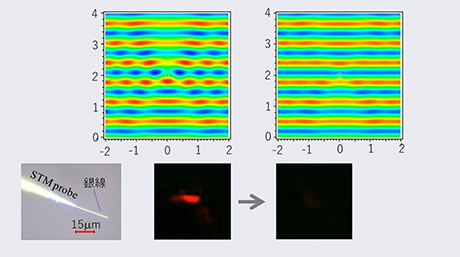

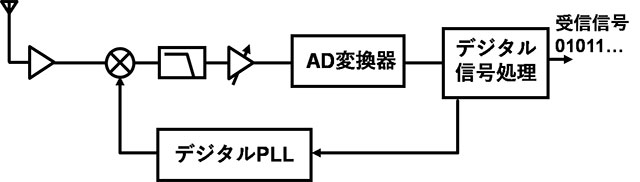

開発したBLE無線機は、キャリア再生[用語6]やアナログデジタル変換[用語7]をPLL回路に担わせることで大幅な消費電力の削減を可能とした(図1)。従来の低消費電力デジタルPLL回路はBLE無線機に必要な低ジッタかつ広帯域な特性を実現できないことが課題だった。これに対し、今回開発したBLE無線機のデジタルPLL回路は、新型DTC(図2)により、低ジッタかつ広帯域な特性を実現し、BLE無線機での利用が可能となった。

(a)従来型BLE受信機の構成

(b)(a)と(c)の中間型

(c)提案型BLE受信機の構成

図1. BLE受信機の構成

特徴:本開発品である提案型BLE無線機では、キャリア再生やアナログデジタル変換をPLL回路に担わせることで大幅な消費電力の削減を可能とした。低消費電力化が可能なデジタルPLL回路において、BLE無線機に必要な低ジッタかつ広帯域な特性を実現できたことにより(c)の構成を実現可能とした。

図2. 新型デジタル時間変換器(DTC)の構成

特徴:従来のDTCでは、大きな容量の充電が必要なため、消費電力が大きく、また、高速な動作も難しかった。提案する新型のDTCでは、小さな容量の充電で済むため、低消費電力かつ高速な動作が可能である。

これにより、従来のBLE無線機の受信に必要な回路規模を半分にし、またアナログデジタル変換器(ADC : Analog-to-Digital Converter)を不要とすることに成功した。またADCとしての性能向上のために、オフセット分を帰還させることで、大幅な分解能の向上を可能とした。最小配線半ピッチ65 nmのシリコンCMOSプロセスで試作したBLE無線機は、送信時に2.9 mW、 受信時に2.3 mWの消費電力で動作する。

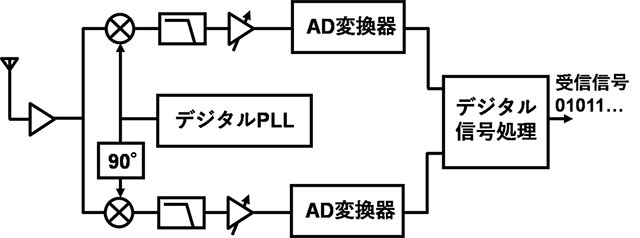

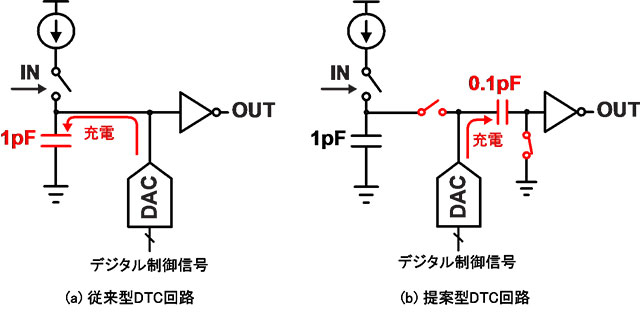

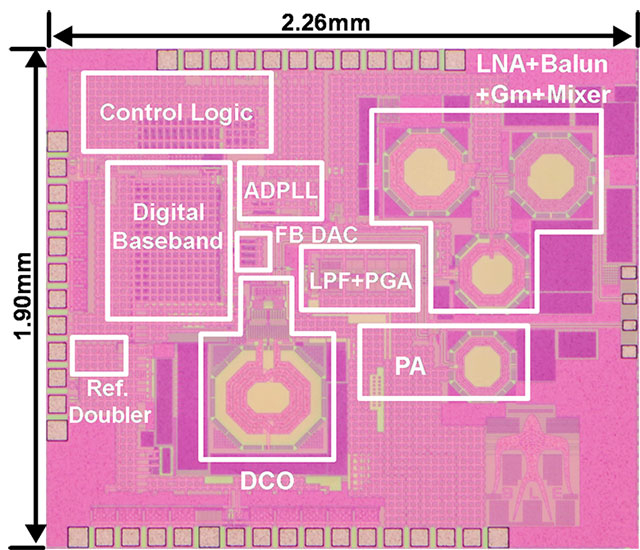

図3にBLE無線機全体の回路ブロック図を示す。送受信回路、局部発振器(PLL)、ベースバンド変復調器などを含み、変復調されたデジタル信号として入出力が可能である。図4にチップ写真を示す。2.26 mm(ミリメートル) x 1.90 mmの小面積で実現した。表1に消費電力の比較を示す。従来、報告があったBLE無線機の半分以下の消費電力で動作を実現した。Bluetooth 4.2(BLE)規格に準拠し、幅広い種類のIoT機器に搭載可能である。

図3. BLE無線機の回路ブロック図

特徴:送受信回路、局部発振器(PLL)、ベースバンド変復調器等を含み、変復調されたデジタル信号として入出力が可能である。

図4. チップ写真

特徴:CMOS 65 nmプロセスにより製造した。

表1. 従来のBLE無線機との消費電力比較

特徴:従来報告のあったものの半分以下の消費電力での動作を実現した。

| 送信 | 受信 | |

| 東工大 ISSCC 2018 | 2.9 mW | 2.3 mW |

| Renesas ISSCC 2015 | 7.7 mW | 6.3 mW |

| Dialog ISSCC 2015 | 10.1 mW | 11.2 mW |

| TI CC2540 *MCU等込み | 63 mW | 58 mW |

| Nordic nRF51822 *MCU等込み | 32 mW | 32 mW |

デジタルPLL回路は単独の評価回路も作成し、同じく最小配線半ピッチ65 nmのシリコンCMOSプロセスで試作、消費電力とジッタ特性において、低消費電力無線向けPLL回路として、世界最高性能を達成している。PLL回路には整数分周型PLLと分数分周型PLL[用語5]がある。整数分周型PLLは基準信号に対して整数倍の周波数を出力するが、分数分周型は分数倍の任意の周波数の出力が可能である。無線通信には分数分周型のPLL回路が必要である。アナログPLLでは分数分周型を比較的容易に実現できるが、低消費電力化で有利なデジタルPLLにおいて分数分周型のものはジッタ特性が劣化しやすく実現が難しいことが課題だった。

今回の研究成果におけるデジタルPLL回路では、新型DTCにより、低ジッタかつ広帯域な特性を低消費電力で実現した。ジッタを消費電力で正規化したPLL FoM[用語9]特性において非常に良好な-246 dBの性能を達成した。従来、同様のFoM性能を達成したものは8.2 mWの消費電力を要したのに対し、8分の1以下の0.98 mWでの動作を実現した。また低消費電力モードでは0.65 mWでの動作も可能である。

今後の展開

本開発品のBLE無線機および極低消費電力のデジタルPLLは、広範なIoT機器への組み込みが可能であり、メンテナンスフリーでの動作を実現することで、IoT機器の爆発的普及への足掛かりとなる技術である。また、特許出願中の新型DTCや、それを用いたデジタルPLLは、要素的回路であるため、無線機以外の幅広い回路用途に利用可能であり、それぞれの用途での性能向上や低消費電力化が期待できる。

発表予定

この成果は2月11日~15日にサンフランシスコで開催される「2018 IEEE International Solid-State Circuits Conference (ISSCC 2018) : 2018年米国電気電子学会 国際固体素子回路会議」の2セッションで発表する。

デジタルPLL技術は講演セッション「Session 15 – RF PLLs」において、「A 0.98 mW Fractional-N ADPLL Using 10 b Isolated Constant-Slope DTC with FoM of -246 dB for IoT Applications in 65 nm CMOS (0.98 mWで動作する分数分周デジタルPLL -10ビットDTCにより-246 dBのFoMを達成-)」の講演タイトルで、現地時間2月13日午後1時半から発表する。BLE無線機等に利用可能な分数分周型のPLL回路において、世界最小消費電力を実現した。

Bluetooth無線機はセッション「Session 28 –Wireless Connectivity」で、「An ADPLL-Centric Bluetooth Low-Energy Transceiver with 2.3 mW Interference-Tolerant Hybrid-Loop Receiver and 2.9 mW Single-Point Polar Transmitter in 65 nm CMOS(送信2.9 mW、受信2.3 mWで動作可能なBLE無線機)」の講演タイトルで、現地時間2月14日午後2時から発表する。

講演1

| 講演セッション : | Session 15 – RF PLLs |

|---|---|

| 講演時間 : | 現地時間2月13日午後1時半 |

| 講演タイトル : | A 0.98 mW Fractional-N ADPLL Using 10 b Isolated Constant-Slope DTC with FoM of -246 dB for IoT Applications in 65 nm CMOS (0.98 mWで動作する分数分周デジタルPLL ー10ビットDTCにより-246 dBのFoMを達成ー) |

講演2

| 講演セッション : | Session 28 –Wireless Connectivity |

|---|---|

| 講演時間 : | 現地時間2月14日午後2時 |

| 講演タイトル : | An ADPLL-Centric Bluetooth Low-Energy Transceiver with 2.3 mW Interference-Tolerant Hybrid-Loop Receiver and 2.9 mW Single-Point Polar Transmitter in 65 nm CMOS (送信2.9 mW、受信2.3 mWで動作可能なBLE無線機) |

用語説明

[用語1] Bluetooth : 2.4 GHz帯の電波を用いる近距離向け無線通信規格。ワイヤレスキーボードなどで幅広く利用されている。旧来のBluetooth規格と、バージョン4.0以降で定義されたBLEは同じ周波数帯で共用できるが互換性を持たない。 Bluetooth Low Energy(Bluetooth LE, BLE) : バージョン4.0以降のBluetooth規格でサポートされる低消費電力での通信が可能なモード。旧来のBluetooth規格とは互換性を持たず、ほぼ別物の規格である。スマートフォンなどに幅広く搭載されており、IoT向けの近距離無線規格として期待されている。バージョン5.0からはデータレートが2倍の2 Mbpsとなるモードや、通信距離を最大400 mまで伸ばせるモードが規定されている。

[用語2] デジタル時間変換器(DTC : Digital-to-Time Converter) : デジタル制御値により、遅延時間が変化する可変遅延回路。デジタル制御遅延回路(DCDL, Digitally-Controlled Delay Line)とも呼ばれる。PLLなどの幅広い回路で利用されている。

[用語3] ジッタ : クロックの重要な特性の一つで、クロック信号の立ち上がりまたは立ち下りタイミングが揺らぐ現象で、本来のタイミングからのずれが統計的にどれぐらいの幅を持つかで評価する。ジッタが小さいほど、クロックの揺らぎが小さい状況を示す。クロックを生成している発振器の位相雑音[用語8] に大きく依存し、位相雑音が低いほど、ジッタも小さくなる。

[用語4] 位相同期ループ(PLL : Phase-Locked Loop) : 集積回路中では正確な周波数基準が作れないため、水晶発振器による基準周波数frefを用い、それをN逓倍して所望周波数N・frefの周波数の信号を得る。PLLには、位相周波数比較器、チャージポンプ、ローパスフィルタを用いるアナログPLLと、時間差デジタル変換器(TDC)とデジタルローパスフィルタを用いるデジタルPLL(オールデジタルPLLとも呼ばれる)が知られている。

[用語5] 分数分周PLL : PLLには、整数分周型と分数分周型がある。整数分周型PLLでは基準信号に対して整数倍の周波数を出力するが、分数分周型では分数倍の任意の周波数の出力が可能である。例えば、水晶発振器から入力される基準クロック周波数が26 MHzの場合、整数分周PLLでは2,418 MHz(93倍)、2,444 MHz(94倍)、2470 MHz(95倍)の生成が可能であるが、分数分周PLLでは2442 MHz(93.923倍)のような任意の小数精度の逓倍動作が可能である。BLE等の無線通信用には、整数分周型ではなく分数分周型のPLLが必要である。アナログPLLでは分数分周型を比較的容易に実現できるが、低消費電力化で有利なデジタルPLLにおいて分数分周型のものはジッタ特性が劣化しやすく実現が難しい。

[用語6] キャリア再生 : 受信機での同期検波による復調動作において、送信機で変調に用いた搬送波(キャリア)に同期した信号が必要である。受信した信号を用いて、そこから同期キャリアを得ることをキャリア再生と呼ぶ。

[用語7] アナログデジタル変換器(ADC : Analog-to-Digital Converter) : 入力されたアナログ値をデジタル値に変換する変換器。変換動作自体については、アナログデジタル変換(AD変換)と呼ばれる。

[用語8] 位相雑音 : 発振器の重要な特性の1つ。必要な周波数の信号に対し、どれだけ不要な周波数のスペクトルを持つかを表す。

[用語9] FoM : FoM(Figure of Merit)の略で、消費電力で規格化したジッタ性能を示す。ジッタと消費電力はトレードオフの関係にあり、発振器の消費電力を増やすとジッタが減少し、消費電力を減らすとジッタが増加する。FoMは、ジッタの標準偏差(δt)と消費電力PDCを用いて、以下の式で定義される。

![]()

ジッタ特性が同じでFoMが10 dB小さければ、消費電力が10分の1であることに相当する。

- 世界最高速!毎秒120ギガビットの無線伝送に成功│東工大ニュース

- 新型デジタル発振器を開発 ―電圧サブサンプリングにより低消費電力、低ジッタ実現―│東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ ― 岡田健一│研究ストーリー|研究

- 東工大教員3名が平成29年度科学技術分野の文部科学大臣表彰で「科学技術賞」を受賞│東工大ニュース

- 松澤・岡田研究室 ―研究室紹介 #1―│東工大ニュース

- 松澤・岡田研究室

- 研究者詳細情報(STAR Search) - 松澤昭 Akira Matsuzawa

- 研究者詳細情報(STAR Search) - 岡田健一 Kenichi Okada

- 研究成果一覧