電気電子系 News

若林研究室 ―研究室紹介 #47―

シリコン・トランジスタ技術を基礎とした低電力・高性能な知的システムデバイスの先行研究

電気電子系では、最先端の研究施設と各分野で活躍中の教員の直接指導により、学生でも世界に誇れる研究成果を出し、自分自身で発表することができます。電気電子系には、大きく分けると「回路」「波動・光および通信」「デバイス」「材料・物性」「電力・エネルギー」の5つのグループがあります。各教員はいずれかのグループに所属しており、研究室単位での研究が行われています。

研究室紹介シリーズでは、ひとつの研究室にスポットを当てて研究テーマや研究成果を紹介。今回は、シリコン・トランジスタ技術を基礎とした低電力・高性能な知的システムデバイスの先行研究を行う、若林研究室です。

デバイスグループ

電気電子コース

研究室:すずかけ台キャンパス・G2棟1002号室

教授 若林整![]()

| 研究分野 | 電子デバイス |

|---|---|

| キーワード | Advanced 3D MISFET(Silicon)、2D FET(MoS2, WS2, HfS2, Black Phosphorous, etc.) |

主な研究テーマ

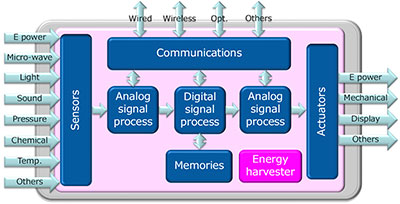

図:知的システムデバイスの信号処理フローと発電システムのブロック図

皆さんの生活に溶け込んだ電子機器に用いられているシリコン・トランジスタからなる集積回路(Integrated Circuits: IC)は、Moore's lawの通りScaling conceptに支えられてLSI (Large Scale Integration)からVLSI(Very LSI)、 ULSI(Ultra LSI)へと進化しています。さらにSmartphone等に搭載されている様に、高周波通信素子や撮像素子(Image sensor)、 Motion sensor等のインターフェースを機能モジュールとして混載するMore than Moore領域へ応用範囲が急速に拡大しています。当研究室では、シリコン・トランジスタ技術[10-18]を基礎として、アプリケーションを意識した高集積・低消費電力・高性能を目指した知的システムデバイスの先行研究を行っています。

最近の研究成果

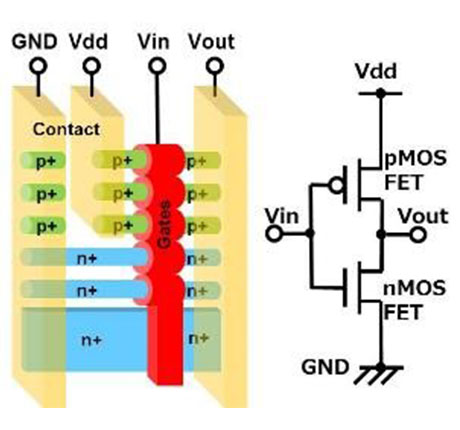

LSI用高度3D高集積化MISFET技術先行研究

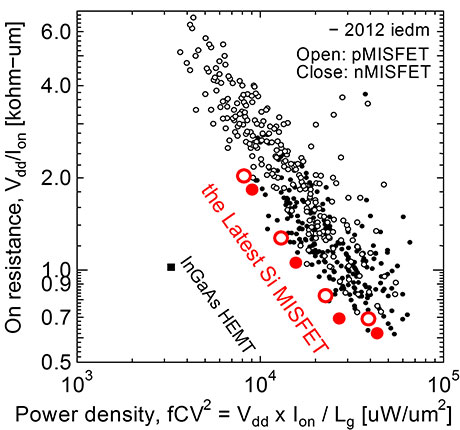

現在でも世界最小のトランジスタの部類にあるゲート電極長が5 nmのシリコンCMOS [15-17]を含む様々な高性能CMOSデバイス動作を実証した経験を基礎に、さらなる高集積化・低消費電力化[18]・高性能化に加え、多機能化を目指した先行研究を行います[1,3,6,8]。例えば右図Benchmark等も用いて研究の意義を明確にしながらデバイス・シミュレーション等を駆使して、効率的にデバイス動作を実証して行きます。特に、高度に3次元高集積化した構造を持つMISFETの性能向上を実現する技術について、公開論文や独自の技術開発だけでなく特許情報等も活用して研究を推進します。

図:シリコンMISFETの性能推移、駆動時抵抗の駆動時消費電力面密度依存性(駆動エネルギー効率を向上させるには左下の方向へ研究を進める必要がある)。

図:シリコンMISFETの性能推移、駆動時抵抗の駆動時消費電力面密度依存性(駆動エネルギー効率を向上させるには左下の方向へ研究を進める必要がある)。

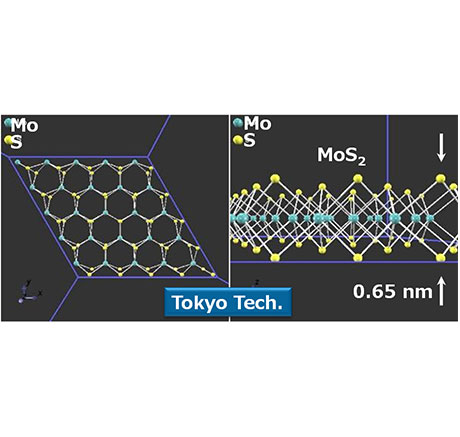

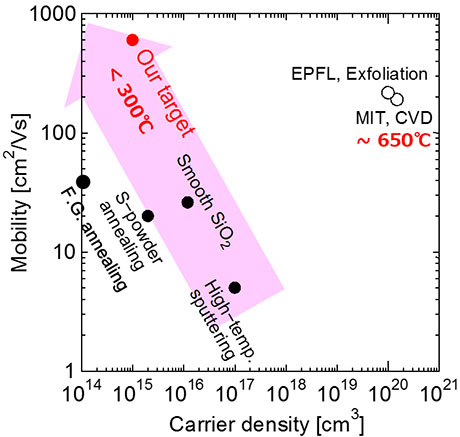

2D FETの応用に関する先行研究

バンドギャップが0 eVであるグラフェンに代わる原子層状半導体である遷移金属ダイカルコゲナイド(MoS2, WS2, HfS2等)を用いた電子デバイスの研究を行っています[2,4,5,7,9]。新材料による新たなデバイス物理を実証・構築し、LSIやディスプレイなどへ応用することを目指して、研究を拡大・加速します。

図:2D層状半導体の例

参考文献

- 1.若林整、「SoC向け先端デバイスの研究開発動向」、SEMICON Japan 2015, 2015/12/18, Invited.

- 2.H. Wakabayashi, "Advanced CMOS Device Technologies Discussed Also with Transition-Metal Di-Chalcogenide (TMDC) Channel," 228th ECS meeting 2015, MA2015-02 1098, Invited.

- 3.若林整、「先端Si-LSIデバイスの現状と今後の展望」、(公社)精密工学会『プラナリゼーションCMPとその応用技術専門委員会』第142回研究会、Invited.

- 4.T. Ohashi, H. Wakabayashi, et.al. "Multi-layered MoS2 film formed by high-temperature sputtering for enhancement-mode nMOSFETs," 2015 JJAP, 54 04DN08, doi:10.7567/JJAP.54.04DN08.

- 5.H. Wakabayashi, "Two dimensional material device technologies," IEEE,EDS,WIMNACT45, Feb.2015, Invited.

- 6.H. Wakabayashi, "Advanced Scaling and Wiring Technology," Tutorials, ADMETAplus2014, Invited.

- 7.T. Ohashi, H. Wakabayashi, et. al., "Multi-Layered MoS2 Thin Film Formed by High-Temperature Sputtering for Enhancement-Mode nMOSFETs," SSDM 2014, pp. 1074-1075.

- 8.H.Wakabayashi, "Progress&Benchmarkingof CMOS-Device Technologies," ICEP2014,FA2-1, Invited.

- 9.H. Wakabayashi, "Progress and prospects of silicon transistors based on junction technologies," IWJT 2013, pp. 98-103, Invited.

- 10.若林整:「V.19.3.1: 論理素子」、「化学便覧応用化学編第7 版」、招待寄稿, 2013.

- 11.若林整:「シリコントランジスタのあゆみと将来」、総合報告(招待解説論文), 応用物理、82 巻、4 号、292 頁、2013.

- 12.H. Wakabayashi, "More-than-Moore Devices based on Advanced CMOS Technologies" (Keynote Address), 2012 AWAD, June 2012, Invited.

- 13.H. Wakabayashi, "CMOS-Device Technology Benchmarks for Low-Power Logic LSIs", G-COE PICE Int'l Symp. and IEEE EDS Mini-Colloquium on Advanced Hybrid Nano Devices: Prospects by World's Leading Scientists, October 2011, Invited.

- 14.H. Wakabayashi, "SONY's outstanding work involving HK-MG on Silicon," 7th International Symposium on Advanced Gate Stack Technology, SEMATECH, 2010, Invited.

- 15.H. Wakabayashi, et al., "Characteristics and Modeling of Sub-10-nm Planar Bulk CMOS Devices Fabricated by Lateral Source/Drain Junction Control," IEEE T-ED, Vol. 53, Issue 9, 2006, pp. 1961-1970, Invited.

- 16.朝日新聞朝刊一面Top「トランジスタ最小化に成功」外、「Sub-10-nm CMOSデバイス」、2003年12月8、9日.

- 17.「電子ビームリソグラフィーで作られた世界最小5 nmトランジスタ」、集英社イミダス2006, p. 859.

- 18.H. Wakabayashi, D.A. Antoniadis, et. al., "Supply-Voltage Optimization for Below-70-nm Technology-Node MOSFETs," IEEE T-SM, Vol.15, No.2, 2002, p. 151-156, Invited.

教員からのメッセージ

- 若林先生より

- 日々指数関数的に増える情報資源を自然に活用する人に優しく豊かな社会の実現に向けて、集積回路技術への期待が高まっています。その一助となることを目指して、実用研究と将来を見据えた探索研究について領域を柔軟に設定して研究を進めます。他方、筒井研究室及び角嶋研究室と強く連携して研究を進めます。すずかけ台の明るく清々しい環境での自由闊達な活動を好む学部/修士/博士学生および研究員を募集しています!共同/委託研究も広く募集していますので、お気軽に御連絡下さい!

電気電子系の全研究室を紹介したパンフレットは広報誌ページでご覧いただけます。

お問い合わせ先

教授 若林整

E-mail : wakabayashi.h.ab@m.titech.ac.jp

Tel : 045-924-5594 FAX : 045-924-5594

※この内容は2016年3月発行の電気電子系パンフレット![]() によります。最新の研究内容については各研究室にお問合せください。

によります。最新の研究内容については各研究室にお問合せください。