電気電子系 News

大見研究室 ―研究室紹介 #24―

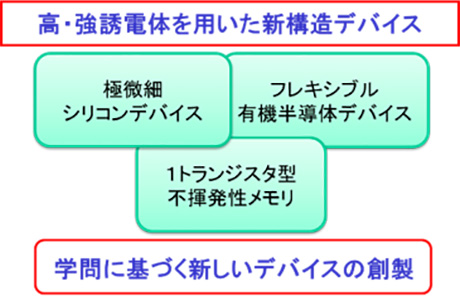

新機能集積化デバイスの創製 ―高・強誘電体を用いた新構造デバイス―

電気電子系では、最先端の研究施設と各分野で活躍中の教員の直接指導により、学生でも世界に誇れる研究成果を出し、自分自身で発表することができます。電気電子系には、大きく分けると「回路」「波動・光および通信」「デバイス」「材料・物性」「電力・エネルギー」の5つのグループがあります。各教員はいずれかのグループに所属しており、研究室単位での研究が行われています。

研究室紹介シリーズでは、ひとつの研究室にスポットを当てて研究テーマや研究成果を紹介。今回は、高清浄な実験環境で新機能半導体デバイスを創製する、大見研究室です。

デバイスグループ

電気電子コース

研究室:すずかけ台キャンパス・J2-1204

准教授 大見俊一郎![]()

| 研究分野 | 集積化電子デバイス、半導体デバイス・プロセス |

|---|---|

| キーワード | シリコンデバイス、有機半導体デバイス、不揮発性メモリ、高誘電率薄膜、強誘電体、シリサイド、原子レベル平坦化 |

| Webサイト | 大見研究室 |

主な研究テーマ

集積化により高性能化する新機能デバイスの創製を目的とした、新しいデバイス構造と作製技術に関する研究を推進する。特に、シリコン酸化膜(SiO2)よりも高い誘電率を持つ高誘電率薄膜や、分極特性によるメモリ機能を有する強誘電体薄膜などの高機能誘電体薄膜を用いて、学問に基づく新構造デバイスの実現を目指す。相補型MOSFET(CMOS)を高性能化する極微細シリコンデバイス、シリコンにはない特徴を持つフレキシブル有機半導体デバイス、ユニバーサルメモリを目指した1トランジスタ型不揮発性メモリを主要な研究テーマとして、本学すずかけ台キャンパスに構築されたクリーンルーム(CR)設備、超純水装置、高純度ガス供給設備などの、恵まれた実験環境を有効に利用して研究を進める。

最近の研究成果

極微細シリコンデバイス

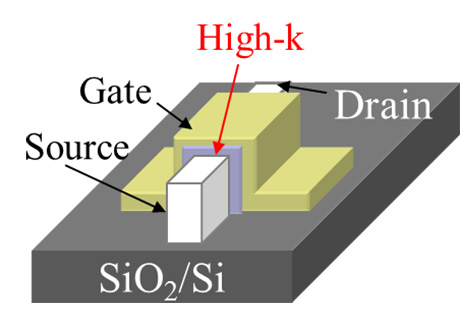

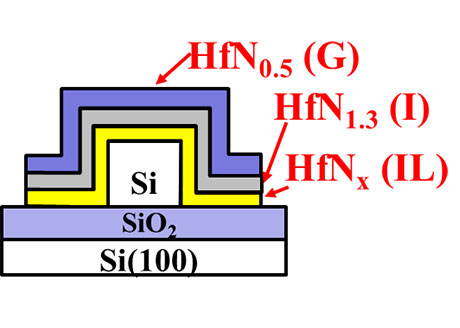

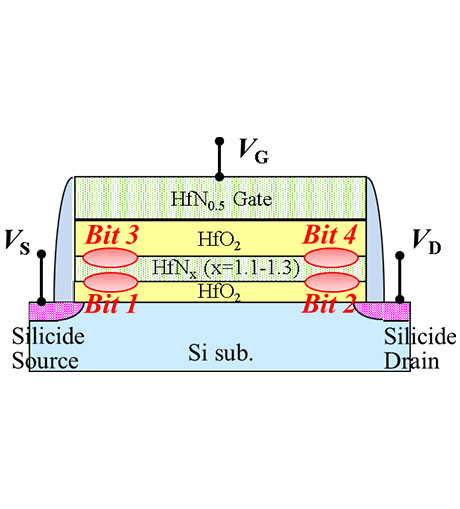

MOSFETのシリコン(Si)チャネル構造を立体化した3次元ゲートMOSトランジスタへの高誘電率窒化ハフニウム(HfN)ゲート絶縁膜の形成に関する研究を進めている(図1)。電子サイクロトロン共鳴(ECR)スパッタ法を用いてHfNx 薄膜の窒素組成を制御することにより、ゲート電極(x <1)とゲート絶縁膜(x >1)をin-situプロセスで形成し、SiO2換算膜厚0.5 nmでリーク電流を劇的に低減したゲートスタック構造を実現してる(図2)。

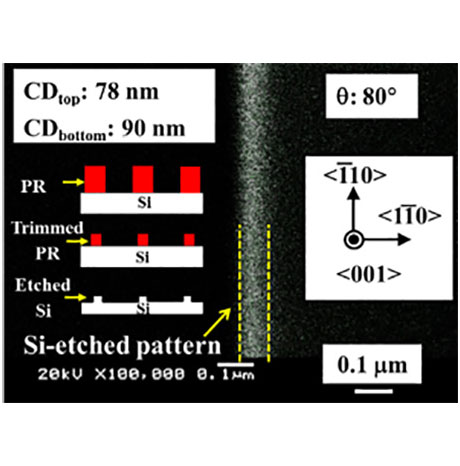

また、Si表面を原子レベルで平坦化することにより、高誘電率ゲート絶縁膜を用いたMOSFETのデバイス特性が向上することを明らかにしている。このSi表面平坦化プロセスを用いて、表面ラフネスを低減した100 nm以下の3次元Siチャネルの形成を進めている(図3)。

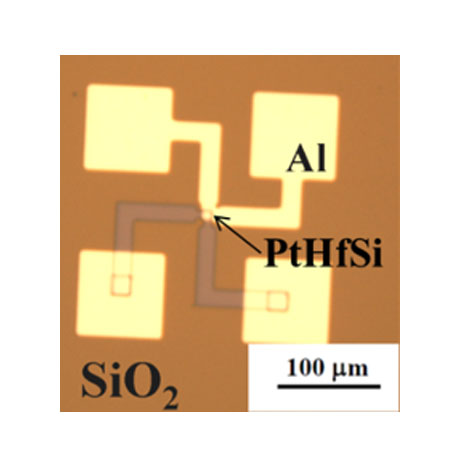

さらに、トランジスタの直列抵抗を低減するために、耐熱性に優れたプラチナシリサイド(PtSi) と、低仕事関数を有するハフニウムシリサイド(HfSi)を混晶化したPtHfSiを形成し、n-Siに対するコンタクト抵抗を10-8Ωcm2に低減することに成功している(図4)。

フレキシブル有機半導体デバイス

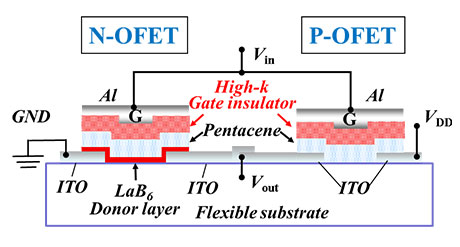

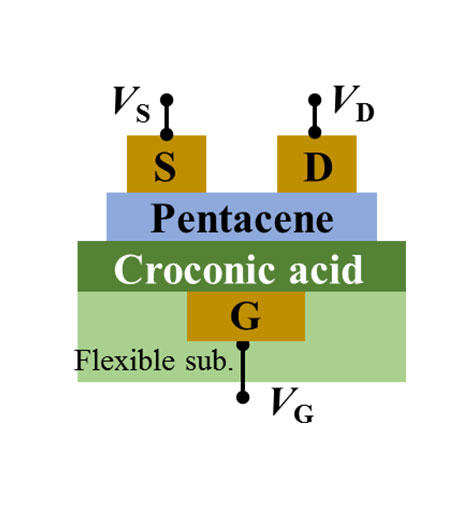

有機半導体は、フレキシブルで軽く、低温形成が可能などの、Siにはない様々な特徴を有しており、新しいエレクトロニクス分野の創製が期待されている。しかし、その材料物性に起因してSiデバイスで用いられるリソグラフィプロセスが適用できないため、有機半導体トランジスタ(OFET)の微細化、高集積化が困難であるという課題がある。この課題を克服するために、図5に示すトップゲート構造を有する有機半導体CMOSの実現に向けた研究を進めている。

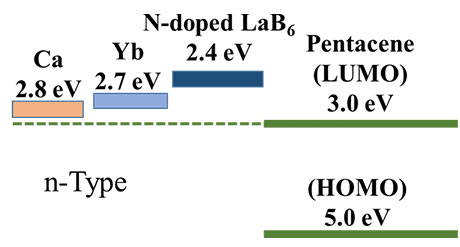

また、集積化に向けた単一有機半導体CMOSに関する研究を行っている。代表的な有機半導体であるペンタセン(C22H14)やルブレン(C42H28)は、ホール移動度に対して電子移動度が著しく低いため、N-OFETにはフラーレン(C60)などの別の材料を用いる必要があり、高集積化が困難となっている。そこで、図6に示すように低い仕事関数(2.4 eV)を有し、大気中で安定な窒素添加LaB6を、ペンタセンの電子供給層として用いることで、光照射下において大気中でのペンタセンの電子電流の測定に初めて成功している。

1トランジスタ型不揮発性メモリ

高速かつ低電圧動作が可能なユニバーサルメモリの創製を目的として、1トランジスタ型不揮発性メモリに関する研究を進めている。まず、フラッシュメモリの高性能化に向けた、 Hf系多層構造によるMONOS型多値メモリに関する研究を行っている(図7(a))。

また、MOSFETのゲート絶縁膜に強誘電体を用いたMFSFETによる1トランジスタ型強誘電体メモリの研究を進めており、Hf系強誘電体薄膜のSi基板上への形成と、低分子有機強誘電体クロコン酸(C6H2O5)の蒸着法による薄膜形成および有機MFSFETの低電圧動作化に関する研究を行っている(図7(b))。

教員からのメッセージ

- 大見先生より

- 自分で考えたデバイスを自分で試作できる。本学の恵まれた実験環境を活かして、思いっきり研究を楽しもう。夢にみるくらい考え抜けば、君のアイディアが世界を変えるかもしれない。

電気電子系の全研究室を紹介したパンフレットは広報誌ページでご覧いただけます。

お問い合わせ先

准教授 大見俊一郎

E-mail : ohmi@ee.e.titech.ac.jp

Tel : 045-924-5481

※この内容は2016年3月発行の電気電子系パンフレット![]() によります。最新の研究内容については各研究室にお問合せください。

によります。最新の研究内容については各研究室にお問合せください。