電気電子系 News

宮本恭幸研究室 ―研究室紹介 #22―

III-V族半導体等を用いた高速・低消費電力電子デバイス

電気電子系では、最先端の研究施設と各分野で活躍中の教員の直接指導により、学生でも世界に誇れる研究成果を出し、自分自身で発表することができます。電気電子系には、大きく分けると「回路」「波動・光および通信」「デバイス」「材料・物性」「電力・エネルギー」の5つのグループがあります。各教員はいずれかのグループに所属しており、研究室単位での研究が行われています。

研究室紹介シリーズでは、ひとつの研究室にスポットを当てて研究テーマや研究成果を紹介。今回は、速くて熱くならない電子デバイスの実現を目指す、宮本恭幸研究室です。

| 研究分野 | 化合物半導体電子デバイス、微細加工プロセス |

|---|---|

| キーワード | InGaAs MOSFET、低消費電力デバイス、トンネルFET |

| Webサイト | 宮本恭幸研究室 |

主な研究テーマ

高度情報化社会では、情報処理量の増大によりIT機器の消費電力が増え続けています。 この消費電力の削減には、電子回路をつくる電子デバイスにおいて、高性能を保ちつつ、消費電力をさげる構造を導入する必要があります。

当研究室では、低消費電力で動作する高速電子デバイス実現の為に、移動度に優れ、 半導体ヘテロ構造の導入が可能なIII-V族半導体を中心として、 低電圧時での高電流密度や低電圧での待機時低消費電力の研究を行っています。 また、耐圧の点で優れたデバイスについての研究も行っています。

最近の研究成果

InGaAs MOSFET

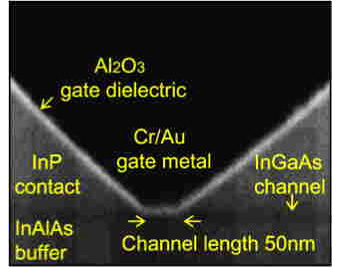

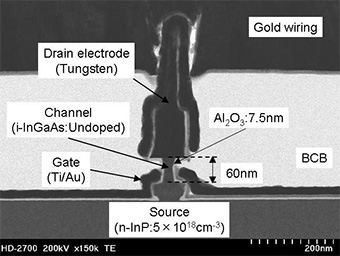

図1.チャネル長50nm素子の電子顕微鏡断面写真

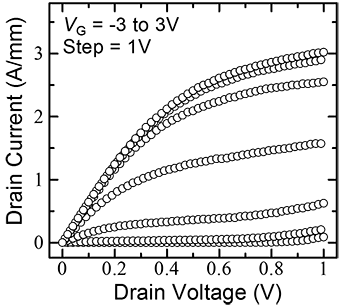

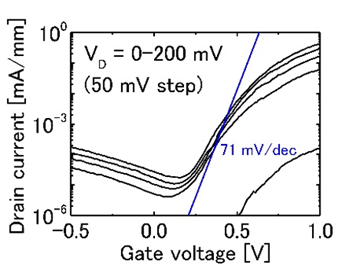

図2.チャネル長50nmの素子のI-V特性

電源電圧=ドレイン電圧を小さくして、大きな電流を流す為には、まずチャネル長を短くすることと移動度を上げることが必要になります。

大学研究室においてチャネル長を短くするのに最も有力なのは、電子ビーム露光法(EBL)による方法であり、当研究室は、数十nmという微細な構造形成が可能になっています。

また移動度を上げる材料としてシリコンに代わるInGaAsが有望視されており、この構造も当研究室では有機金属気相成長装置という装置で望む薄膜構造をエピタキシャル成長できます。

さらに高い電流密度を保つ為にはソースから充分な電子が供給される必要があります。そこで、エピタキシャル成長による高濃度ソースを持ったInGaAs MOSFETを提案・作製しています。チャネル長50nmのFETでは、ドレイン電圧0.5Vにおいて2.4A/mmという高電流密度を示せました。これは国際半導体技術ロードマップ(ITRS)において2018年以降に予定されているInGaAs MOSFETの目標値(2.2A/mm@0.63V)を世界で始めて上回ったものです。

またさらなる微細化(現在最小値13nm)や三次元構造デバイスの研究も行っています。

原子層状半導体HfS2 によるFET

FETにおいて短チャネル効果抑制のためのチャネルの究極の薄層化として、積層構造型半導体材料の導入が考えられ、代表的な層状物質であるグラフェンは単純な周期構造ではバンドギャップを持たない欠点があることから、バンドギャップを有する層状半導体が期待されています。

当研究室では、単分子層で高い電子移動度(1,800 cm2/Vs)とSiと同等の禁制帯幅(1.2 eV)が予測されている遷移金属カルコゲナイドHfS2において世界で初めてトランジスタ動作を実現しています。

ヘテロ構造を持った縦型InGaAsFET

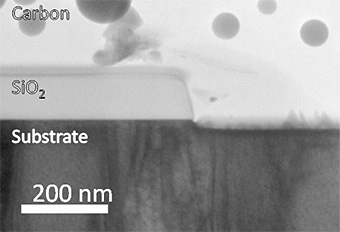

図3.15nm幅のメサを持つ縦型InGaAsFETの透過電子顕微鏡断面像

図4.GaAsSb/InGaAsチャネル縦型トンネルFETのサブスレッショルド特性

縦型トランジスタ構造では、異種の材料組合せ(ヘテロ接合)を導入することにより、電子の走行する位置によってもっとも適した特性を持つ構造を実現することができます。例えば、ヘテロ接合によるバンド不連続での電子を加速するランチャを導入した縦型InGaAs FETでは、チャネル長60nm、チャネルメサ幅15nmの素子を作製し、7MA/cm2の電流密度を確認しています

現在当研究室では、この素子作製プロセスを低電圧においても待機電力を下げるトンネルFET構造に応用しています。InGaAsをチャネルとすることはゲートオーバードライブ電圧(有効ゲート電圧・実効ゲート電圧とも呼ばれます)や ドレイン電圧を低くして高い電流を得るには有用ですが、電圧を下げるためにもう一つ必要なのは、しきい値自身を小さくことです。その為には、オフ状態でのリーク電流(待機時電流)に注意を払う必要があります。通常しきい値以下でのリーク電流の変化は、サブスレッショルドスロープと呼ばれるチャネル/ソース間電位の60mV変化で一桁以下しか減少しないという熱限界があり、低電源電圧でオフすべき電流量を下げるには、この熱限界を打ち破ることが必要です。 バンド間トンネリングによりキャリヤを注入するトンネルFETはこの熱限界を打ち破れると期待されていますが、一般的なシリコンはトンネル抵抗が高く、高電流密度を実現することが困難です。

そこで当研究室では、GaAsSb/InGaAsによるタイプIIと呼ばれる価電子帯と伝導帯があらかじめ近づいたヘテロ接合を導入しています。現時点で得られた最小のサブスレッショルドスロープは71mV/decであり、熱限界はまだ破れていませんが、タイプII型ヘテロ接合を用いた縦型FETとしては世界最小の値を得ています。今後、絶縁膜の改善をおこなうことで、さらに急峻な変化を目指します。

超格子構造によるスティープスロープFET

急峻なサブスレッショルド特性と高オン電流を両立させるための構造として、超格子をソースに導入したFETについて、理論的計算を行うとともに、超格子構造を導入したダイオードを作製し、その実験的な検証も行っています。

GaN系HEMTの高性能化

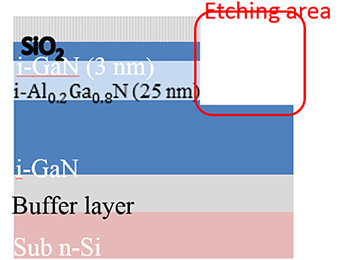

電源電圧などの高電圧の領域においては、耐圧の点でSiよりもバンドギャップが広い化合物半導体であるGaNを用いたデバイスが有望です。当研究室では、GaN HEMTについてしきい値を作製時に制御する為の新たなプロセスの開発を行っています。

またGaN HEMTの高周波応用に向けた研究も行っています。(本研究は三菱電機との共同研究です。)

図5.デジタルエッチングされたAlGaN層の断面TEM像とその模式図

教員からのメッセージ

- 宮本先生より

- 自分で思いついた新しい素子を、自分で設計し、自分の手で作製し、自分でその素子の測定・評価をするということは、技術者・研究者としての楽しみの一つです。我々の研究室においては、他ではなかなか使えない世界最高水準の電子ビーム露光装置や結晶成長装置などを目一杯使って、その楽しみを味わって貰いたいと思っています。

電気電子系の全研究室を紹介したパンフレットは広報誌ページでご覧いただけます。

お問い合わせ先

教授 宮本恭幸

E-mail : miya@pe.titech.ac.jp

Tel : 03-5734-2572

※この内容は2016年3月発行の電気電子系パンフレット![]() によります。最新の研究内容については各研究室にお問合せください。

によります。最新の研究内容については各研究室にお問合せください。