電気電子系 News

サブテラヘルツ帯CMOS ICで640 Gbpsの無線伝送に成功

超高速無線通信を用いた遠隔医療や自動運転の実装に前進

要点

- 世界最速の640 Gbpsの伝送速度を達成するCMOS送受信ICを開発

- 次世代無線通信での周波数候補であるD帯(110-170 GHz)で動作

- 超高速通信を用いた新サービスの創出や次世代通信インフラへの応用を期待

概要

東京工業大学 工学院 電気電子系の岡田健一教授(電気電子コース 主担当)と情報通信研究機構(NICT)の研究チームは、サブテラヘルツ帯[用語1]CMOS送受信ICを開発し、毎秒640ギガビットの無線伝送に成功した。

次世代無線通信では、幅広い周波数を利用できるサブテラヘルツ帯を用いて、100 Gbps以上の超高速無線通信を実現することが期待されている。しかしながら、従来、無線通信に使用していた周波数に比べ、非常に高い周波数であるため、無線デバイスの性能劣化やコスト増加が課題であった。特に、広帯域にわたり、多値変調[用語2]に要求される高いSNR[用語3]を実現するのが困難であった。

今回の研究では、D帯[用語4]向けのCMOS送受信ICを開発した。安価で量産性に優れる65 nm CMOSを採用し、送信と受信の高周波部をそれぞれ1チップに集積した。広帯域・高SNRに適した回路アーキテクチャを考案し、高精度モデリング・設計技術により、114-170 GHzの56 GHzにわたる超広帯域特性を実現した。

作製した送受信機を用いて無線伝送測定を行ったところ、送受信一対のアンテナを用いて200 Gbpsの伝送速度を達成した。また、4×4 MIMO[用語5]適用時に640 Gbpsの伝送速度を達成した。さらに、距離15 mにおいて120 Gbpsの伝送速度を達成した。これらの特性は、現行5Gの伝送速度の10-100倍に相当するものであり、また、CMOSなど汎用的な技術で実現していることから、XR[用語6]を用いた新サービスの創出や、それを支えるx-Haul[用語7]など次世代通信インフラの実現と普及に貢献することが期待される。

本研究成果は、6月16日~20日に米国ホノルルで開催された「2024 IEEE Symposium on VLSI Technology & Circuits」で発表された。また、この発表論文は同国際学会の注目論文の一つに選定されている。

背景

次世代無線通信では、広い周波数帯域を利用できるサブテラヘルツ帯(100-300 GHz)を用いて、5Gの10倍に相当する100 Gbps級の超高速無線通信の実現を目指している。これにより、増加を続ける通信トラフィックに対応することが期待されている。しかしながら、サブテラヘルツ帯は、現在5G(28GHz帯)やWi-Fi(60GHz帯)で使用されているミリ波帯に比べても非常に高い周波数帯であるため、信号の損失が大きくなることや、波長が短くなることに伴い無線送受信機の設計や製造の難易度が大幅に上がり、性能の劣化やコストの増加につながる。そのため、サブテラヘルツ帯通信の実用と普及に向けては、高周波集積回路(IC)技術を用いた低コストで高性能な無線送受信機の実現が強く求められている。

100 GHzを超える周波数帯においては、化合物半導体を用いたデバイスが高い出力電力などの優れた特性を示すことが実証されているが、制御用デジタル回路との集積が困難であるという課題がある。一方で、近年、量産性や集積性に優れるシリコンCOMSやシリコンゲルマニウム(SiGe)を用いたサブテラヘルツ帯ICの報告も増えている。しかしながら、数十GHzの広い帯域幅にわたって、16QAMや32QAMなどの多値変調に要求される高SNRを実現するのが困難で、サブテラヘルツ帯の広い周波数帯域の利点を十分に生かせていなかった。

研究成果

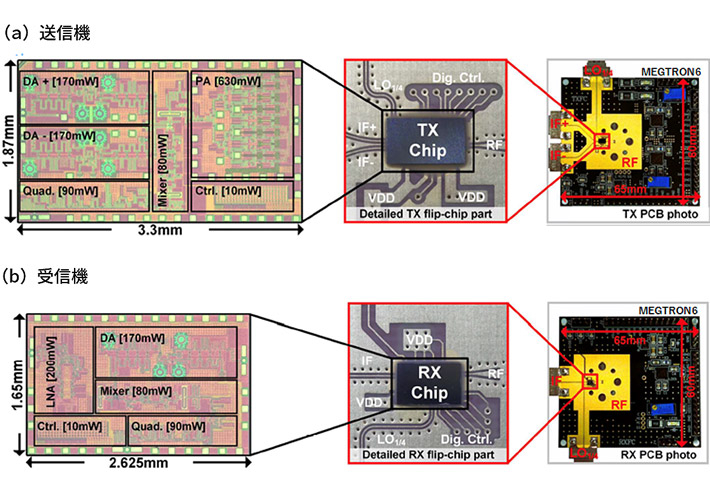

今回開発したのは、D帯(110-170 GHz)向けの送信ICと受信ICからなるチップセットである。プロセスは、安価で量産性・集積性に優れる65 nmシリコンCMOSを採用した。送信ICと受信ICは、高出力増幅器(PA)/低雑音増幅器(LNA)、周波数変換器(Mixer)、分布型増幅器(DA)、周波数逓倍器(Quadrature)等をそれぞれ1チップに集積している(図1左)。チップサイズは、送信ICが1.87 mm×3.30 mm、受信ICが1.65 mm×2.60 mmである。

回路設計

回路設計においては、サブテラヘルツ帯の優位性を生かすために、高精度なデバイスモデリングに基づいて、それぞれの回路ブロックにおいて広帯域・高SNRを実現する回路アーキテクチャを考案した。具体的には、8パス低Q電力合成による電力増幅器、2パス低Q電力合成による低雑音増幅器、広帯域インピーダンス変換ミキサ、コモンソース型のカスケード分布型増幅器[用語8]を提案し、広帯域かつ高SNRな特性を実現した。開発したCMOS送受信ICを評価し、56 GHz (114 GHzから170 GHzまで)の極めて広い帯域幅にわたって、高いSNRを有していることを確認した。

ICチップの送受信機への実装

作製したICチップは、プリント基板(PCB)上にフリップチップ実装[用語9]した(図1中)。さらに、外部アンテナと接続して無線伝送評価するために、PCB上で、伝送線路から導波管へ変換する機構を開発した(図1右)。変換部の損失は、約4 dBと小さく抑えられている。この構成により、アンテナとのインターフェースは標準的な導波管となり、用途に応じて各種アンテナとの接続が可能である。

図1. 開発したD帯送受信機

(左)CMOS 送受信IC(中)フリップチップ実装したICチップ(右)ボード全体

送受信機の性能評価

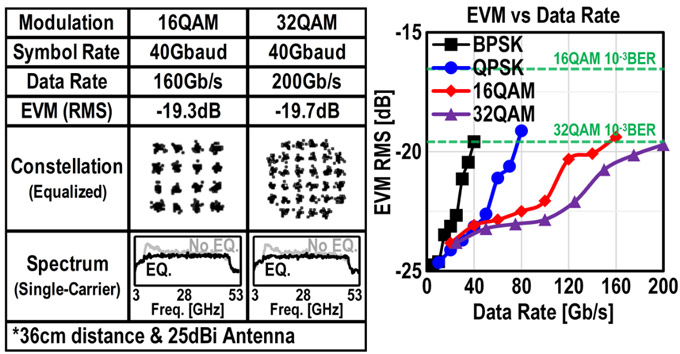

開発したD帯送受信機を利得25 dBiのアンテナに接続して、実際に電波を発射して無線伝送測定を行った。距離36 cmで、シンボルレート40 Gbaud、32QAMの変調信号を用いて評価したところ、10-3以下のビットエラーレート(BER)を達成するのに必要な変調精度(EVM(RMS)<-19.6 dB)を満足していることを確認した(図2)。これは、伝送速度200 Gbpsに相当し、現行5Gの最大伝送速度の10倍以上に相当する。さらに、垂直・水平偏波多重[用語10]を用いて、4×4 MIMO測定を行ったところ、16QAM変調時に4チャネルそれぞれ160 Gbpsの伝送速度を確認し、合計で640 Gbpsを達成した。これらの特性は、集積回路で実現した無線送受信機としては、世界最高の伝送速度となる。

図2. 近距離(36 cm)での無線伝送測定の結果

- (左)16、32QAM変調時の変調精度(EVM)、コンスタレーション、スペクトル

- (右)変調信号とシンボルレートを変えたときの伝送速度とEVMの関係

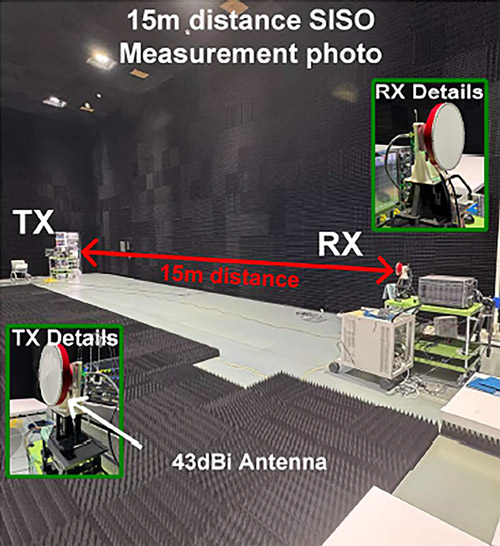

また、同じD帯送受信機に高利得(43 dBi)のアンテナを接続し、NICTが保有する長距離伝送用の測定環境(B5G電波暗室棟)と測定技術を用いて、見通し内15 mの距離で無線伝送測定を行った(図3)。その結果、16QAM変調時に120 Gbpsの伝送を実証した。

図3. 伝送距離15 mでの無線伝送測定の様子

社会的インパクト

今後、自動運転や遠隔医療などの普及や、XRを用いた新サービスの出現等により、高速・大容量通信の需要は増加し続けることが予想される。本研究で達成した伝送速度は、現行の5Gの10-100倍に相当するものであり、また、安価で量産性に優れるCMOSプロセスで実現していることから、こうした通信需要に対応した無線デバイスや、それを支える通信インフラの実現と普及に大きく貢献できると考えられる。

今後の展開

今回開発したD帯送受信機は、汎用性や歩留まりの高い半導体プロセスや実装技術、標準的なインターフェースを採用しており、再現性・拡張性が高い。そのため、サブテラヘルツ帯通信の有望な応用先の一つと期待されるx-Haul向け固定無線通信などに向け、大規模化し、さらなる長距離・大容量伝送を目指す。

- 付記

本研究は、総務省委託研究「テラヘルツ波による超大容量無線LAN伝送技術の研究開発(JPJ000254)」の成果の一部である。

- 用語説明

[用語1] サブテラヘルツ帯 : 無線通信における周波数帯の一つで、通常、100 GHzから300 GHzの周波数帯を指すことが多い。

[用語2] 多値変調 : デジタル通信において、1つのシンボル(信号の状態)に複数のビットを割り当てる変調方式。16QAM(Quadrature Amplitude Modulation)では、シンボル当たり4ビット、32QAMでは5ビットの情報量を伝送することができる。

[用語3] SNR : Signal-to-Noise Ratio、信号対雑音比。所望信号と雑音の強度の比率を示す指標。SNRが高いほど、通品品質が良好であることを示す。

[用語4] D帯 : サブテラヘルツ帯の一部で、110 GHzから170 GHzの周波数帯。6Gで用いられる有力な候補周波数帯の一つ。

[用語5] MIMO : Multiple-Input Multiple-Outputの略。送信機と受信機の双方で複数のアンテナを用いて送受信し、通信容量を増やす無線通信技術。

[用語6] XR : Cross Realityの略。現実世界と仮想世界を融合することで、現実では知覚できない新たな体験を創造する技術の総称。VR(仮想現実)、AR(拡張現実)、MR(複合現実)などが含まれる。

[用語7] x-Haul : 移動通信システムにおいて、アクセスポイントとデータセンター間を接続するトランスポート・ネットワークの総称。ネットワーク形態により、フロントホール、ミッドホール、バックホールなどに分類される。

[用語8] 分布型増幅器 : トランジスタの寄生容量を伝送線路の一部として、カットオフ周波数の高い伝送線路を構成することにより、広帯域な特性を実現する増幅器の構成。

[用語9] フリップチップ実装 : 半導体チップに接続用バンプを形成し、反転(フリップ)して基板に接続、実装する方法。ワイヤー接続に比べ、実装面積削減や接続に起因する性能劣化を抑えられる利点がある。

[用語10] 偏波多重 : 同一周波数で異なる偏波モードに独立な信号を乗せて伝送し、伝送容量を向上する通信技術。偏波モードの組み合わせには、直線偏波における垂直と水平、円偏波における右旋と左旋などがある。

- 発表

本研究成果は6月16日からホノルルで開催された国際会議2024 IEEE Symposium on VLSI Technology & Circuitsで講演セッションとデモセッションで発表された。また、本研究は、同国際会議の論文委員会において高く評価され、回路セッション全138件の発表のうち11件の注目論文の一つに選定されている。

| タイトル : | A 640-Gb/s 4×4-MIMO D-Band CMOS Transceiver Chipset |

| 講演セッション : | C9 Wireless Transceivers |

| 講演時間 : | 現地時間 6月18日 午後3時50分~4時15分 |

| デモ時間 : | 現地時間 6月17日 午後5時30分~7時30分 |

| 会議Webサイト : | 2024 IEEE Symposium on VLSI Technology & Circuits |

- Beyond 5Gに向けた新規デジタル位相同期回路を開発|東工大ニュース

- オールCMOSの300 GHz帯フェーズドアレイ送信機を開発|東工大ニュース

- 300GHz帯でのビームフォーミングと高速データ伝送に成功|東工大ニュース

- 6G向け100 Gbps超の超高>速サブテラヘルツフェーズドアレイ無線機を開発|東工大ニュース

- 低軌道衛星コンステレーションに向けた耐放射線Ka帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 小型地球観測衛星搭載用のKa帯フェーズドアレイ無線機の低消費電力化に成功|東工大ニュース

- 新アーキテクチャのデジタル位相同期回路を開発|東工大ニュース

- Beyond 5Gの端末機に向けたマルチバンドフェーズドアレイ受信ICを開発|東工大ニュース

- 超小型衛星搭載用Ka帯無線機の開発に成功|東工大ニュース

- 無線電力伝送と無線通信双方に同時対応するミリ波帯フェーズドアレイ無線機の開発に成功|東工大ニュース

- 5GおよびBeyond 5Gの基地局に向けた高効率ミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 超高速ビームフォーミングが可能なミリ波帯フェーズドアレイ無線機を開発|東工大ニュース

- 電源不要のミリ波帯5G無線機の開発に成功|東工大ニュース

- テラヘルツ帯でのフェーズドアレイ無線機を実現|東工大ニュース

- 300 GHz帯無線トランシーバの省電力化に成功|東工大ニュース

- Ka帯衛星通信向け無線ICの開発に成功|東工大ニュース

- 東工大の教職員3人に2023年IEEEフェローの称号を授与|東工大ニュース

- 「異分野融合研究支援」を創設 3チームに授与|東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ — 岡田健一|研究ストーリー|研究

- 岡田健一 Kenichi Okada|研究者検索システム 東京工業大学STARサーチ

- 岡田研究室

- 電気電子コース(大学院課程)|教育|工学院 電気電子系

- 電気電子系(学士課程)|教育|工学院 電気電子系

- 情報通信研究機構(NICT)

- 研究成果一覧