電気電子系 News

エネルギー最小点で動作する並列演算ニューラルネットワーク・アクセラレータ技術を開発

AI半導体のエネルギー効率最大化技術

ポイント

- エネルギー最小点(EMP)で推論動作可能な並列演算プロセッシング・イン・メモリ(PIM)型のニューラルネットワーク(NN)アクセラレータ・マクロを開発。

- 積和(MAC)演算の並列化によって、EMPを低減させ推論のエネルギー効率を飛躍的に増大できる技術を開発。

- NNアクセラレータの課題である、高い推論能力と大幅な低消費電力化の両立を実現。

概要

東京科学大学(Science Tokyo)総合研究院 未来産業技術研究所の菅原聡准教授と塩津勇作研究員らは、エネルギー最小点(EMP)[用語1]で推論動作を行うことでエネルギー効率を大幅に向上できる、並列演算プロセッシング・イン・メモリ(PIM)型のニューラルネットワーク(NN)アクセラレータ[用語2]・マクロ[用語3]を開発しました。

NNアクセラレータの高性能化では、演算能力(TOPS[用語4])を維持したまま消費電力を低減させることが求められるため、エネルギー効率(TOPS/W[用語4])の向上が必要になります。PIM技術はNNアクセラレータのエネルギー効率の改善に有効ですが、本研究では、PIMをエネルギー最小点(EMP)で動作させることによってエネルギー効率を最大化させるだけでなく、積和(MAC)演算の並列化によって、PIMのエネルギー効率の最大値を大幅に増大できる技術を開発しました。

本技術では、菅原准教授と塩津研究員が既に開発したEMP動作が可能な特殊なSRAMを用いて、任意のサイズ・形状のネットワークを実現できるアクセラレータ・マクロとして開発しました。このSRAM部には並列読出しを実装してもメモリ面積を増加させない新たなメモリアレイ構造も導入しました。今回開発したPIM型NNアクセラレータ・マクロを用いてMAC演算の並列数を増大させることで、演算能力を向上させるだけでなく、EMPをより低電圧側にシフトさせ、エネルギー効率を大幅に向上できることが明らかになりました。開発した8並列のMAC演算ユニットを有する2値化NNアクセラレータ・マクロでは、低減されたEMPで164 TOPS/Wもの高いエネルギー効率を達成しました。

本成果は、IEEE(米国電気電子学会)の「IEEE Journal on Exploratory Solid-State Computational Devices and Circuits」に3月10日付で掲載されました。

背景

AI半導体として用いられるニューラルネットワーク(NN)アクセラレータの高性能化においては、演算能力(TOPS)とエネルギー効率(TOPS/W)の向上が重要になります。特に演算能力を維持したまま消費電力を低減させるためにはエネルギー効率の向上が必要になります。これまで、NNアクセラレータはハードウェアの工夫により高性能化を実現してきました。例えば、NNアクセラレータにおける重要演算である積和(MAC)演算を大規模に並列化することや、MAC演算の実行を汎用の演算器からより効率の良い専用の演算器に変更すること、さらには、processing-in-memory(PIM)と呼ばれる新たなハードウェアを用いることなどが試みられています。

PIM型のハードウェアでは、メモリアレイ内またはこの近傍に演算ユニットを配置することで、バスを介したデータ転送を用いることなく、データ処理を可能にしています。PIMのNNアクセラレータ応用でも同様に、バスを介することなくメモリにある重みデータを取り出し、MAC演算を行うことで、エネルギー効率を向上できます。また、PIM型ハードウェアはバスのビット幅による制約を受けないことから、NNアクセラレータの演算能力の向上に重要なMAC演算の並列化に適したハードウェアでもあります。特に、メモリにSRAMを用いたPIM型NNアクセラレータは現状のロジックCMOS技術で実装が可能なため、応用上極めて重要です。

NNアクセラレータの性能向上における重要課題は、消費電力の削減です。先に述べたように、演算能力を維持したまま消費電力を削減するためには、エネルギー効率の向上が必須です。これには、エネルギー最小点(EMP)となる駆動電圧を用いた推論動作が極めて効果的になります。CMOSロジックシステムのEMPは動作時電力と待機時(リーク)電力が拮抗する電圧付近で生じ、0.25-0.4 V程度となることが知られています。このような低電圧となるEMP動作では、SRAMを含む一般的なメモリの動作信頼性を確保することは困難です。したがって、EMPで動作するPIM型NNアクセラレータは容易には実現できませんでした。

研究成果

本研究では、これまでに菅原准教授と塩津研究員が開発してきたEMP動作可能なSRAMを用いて、PIM型のNNアクセラレータ技術を開発しました。MAC演算の並列数を増大させることで、演算能力を向上させるだけでなく、EMPをより低電圧側にシフトさせて、エネルギー効率を大幅に向上できる技術です。

このNNアクセラレータ技術は、任意のサイズ・形状のネットワークを実現できるアクセラレータ・マクロとして開発しました。このマクロ技術では、複数のマクロを適宜組み合わせることで任意のネットワークを構成できます。今回は2値化NN(BNN)で実装を行いましたが、INT4、INT8と呼ばれるより精度の高い推論用に構成することも可能です。

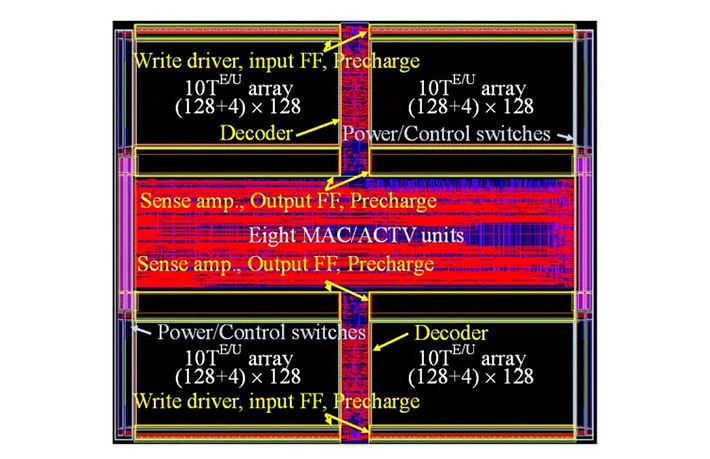

図1に開発した並列化PIM型NNアクセラレータ・マクロのレイアウトを示します。このマクロでは8並列のMAC演算を実現できます。SRAMには菅原准教授と塩津研究員が開発したEMP動作を実現できるメモリセルを用いました[参考文献1、2]。このメモリセルはEMP動作だけでなく、超低電圧リテンションといった特殊な動作モードによって待機時電力も削減できます。一般にメモリの並列読み出しにはマルチポート・セルといった特殊なセルが用いられますが、今回開発したマクロではマルチポート・セルを用いることなく並列化する技術を新たに提案しました。このため、メモリ部のセルアレイ部の面積は、並列化を行わない場合(既開発の1並列のPIM型NNアクセラレータ・マクロ[参考文献2])と変わりません。

- 図1.8並列PIM型BNNアクセラレータ・マクロのレイアウト

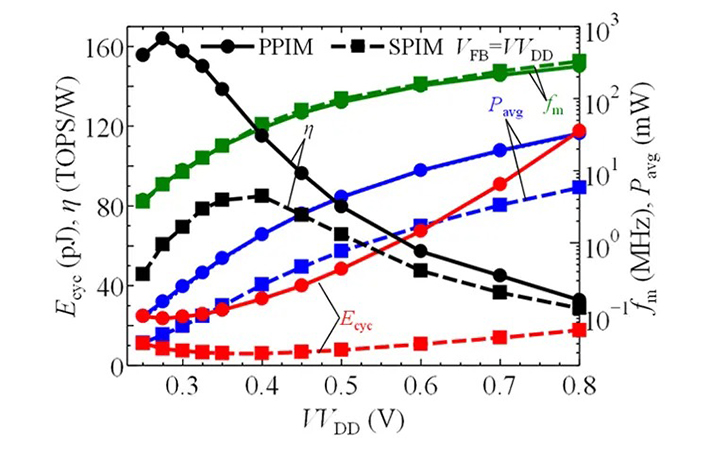

次に、このマクロを用いて推論動作時の性能評価を行いました(図2)。従来の1並列PIM型マクロ(SPIM)のEMPは0.4 Vである一方、今回開発した8並列PIM型マクロ(PPIM)のEMPは0.275 Vに低減できました。このときPPIMのエネルギー効率ηは大幅に増加し、164 TOPS/Wに達しました。この値はSPIMと比較して2倍程度に向上しています。EMPは動作時電力と待機時(リーク)電力が拮抗する電圧付近で生じることから、PIMの並列読み出しを行うことで、EMPを低電圧側に移動させることができます。また、EMPが約0.1 V変化するだけでエネルギー効率が大幅に改善できることが分かります。今回設計したセルでは十分に低い不良率(6σ不良率)を満たすことができるのは0.35 Vまでですが、この電圧でも、ηは100 TOPS/W以上の十分高い値を実現できます(138 TOPS/W)。また、~0.3 V程度でも6σ不良率を満足できるSRAMセルも開発済みです。今後、このセルを用いることで、先に述べたような150 TOPS/W以上のエネルギー効率を高い信頼性で実現できると予想できます。

- 図2. 今回開発したマクロにおける動作周波数fm(緑)、平均電力Pavg(青)、消費エネルギーEcyc(赤、1サイクル当たり)、推論のエネルギー効率η(黒)の仮想電源電圧VVDD依存性。実線は今回開発した8並列PIM型マクロ(PPIM)、破線は従来の1並列PIM型マクロ(SPIM)。

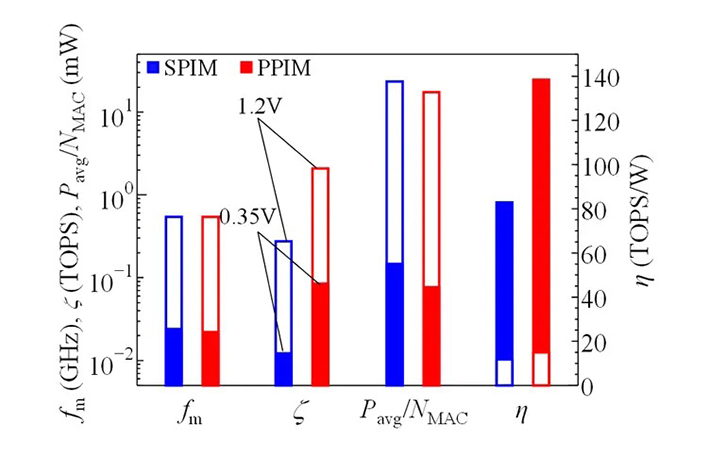

図3に、SPIMとPPIMにおけるPavgを並列数(NMAC)で規格化した電力Pavg/NMAC、演算能力ζを示します。また、同図には動作周波数fm、エネルギー効率ηも示してあります。ここでは電源電圧(仮想電源電圧VVDD)が1.2 Vと0.35 Vの場合を比較しています。SPIMと比較してPPIMは1.2V動作、0.35 V動作どちらにおいてもfmはわずかに低下しますが、8並列MAC演算の導入によってζは大きく向上しています。また、MAC演算あたりの電力Pavg/NMACは、PPIMではSPIMの場合と比較して、1.2 V動作で25%程度、0.35 V動作では~50%程度も低減できます。これらから、PPIMではEMP近傍である0.35 V動作でηを大幅に向上できることが分かります(1.2 Vのηから10倍)。以上のように、MAC演算を並列化したPIM (PPIM)では、EMPの低減によるエネルギー効率の増大が可能であることが分かりました。

- 図3.SPIMとPPIMにおける1.2 V動作と0.35 V動作の規格化平均動作時電力Pavg/NMAC、動作周波数fm、演算能力ζ、エネルギー効率η

社会的インパクト

これまで、NNアクセラレータは、演算の並列化(GPU)、演算部の専用化(カスタムプロセッサ)、さらには重みデータの高エネルギー効率活用(PIM)など、ハードウェアの工夫によって高性能化を試みられてきました。本研究で開発したPIM型のNNアクセラレータ技術は、EMPによってエネルギー効率を最大化させるといった全く別のアプローチによる高性能化技術です。このベースとなる技術はEMPでの動作においても高い信頼性(高いノイズマージンと高いばらつき耐性)を確保できるメモリ技術です。また、今回開発した技術はMAC演算の並列化によってEMPを低減させエネルギー効率をさらに増大させる新しい技術でもあります。これらのメモリ技術やエネルギー効率増大技術は、先に述べたNNアクセラレータに関する各種ハードウェアにも応用可能です。

今後の展開

今後は、さらにMAC演算の並列数を増やしたPIMマクロの開発を行います。また、本技術を拡張して、INT4、INT8の推論に対応するPIMマクロ技術や、GPUやカスタムプロセッサにも応用できるマクロ技術の開発を行います。

- 参考文献

- 用語説明

| [用語1] | エネルギー最小点(EMP):CMOSロジックシステムで消費される全エネルギーは回路動作に基づく動作時エネルギーと、トランジスタのリークによって生じる待機時エネルギーからなる。これらはそれぞれ異なる電圧依存性を有することから、全エネルギーは特定の電圧で最小値をとる。この全エネルギーが最小となる動作点がEMPである。EMPを動作電圧とすることで、エネルギー効率を最大化できる。 |

|---|---|

| [用語2] | アクセラレータ:特定の処理を高速化できるハードウェアまたは演算システム。特に、AIシステムでは、各種ニューラルネットワーク(NN)による推論処理に特化した専用のアクセラレータが用いられることが多い。AI半導体の分野では、NNアクセラレータやAIアクセラレータとも呼ばれる。 |

| [用語3] | マクロ:特定の機能を持つ回路ブロック。例えば、SRAMでは比較的小さな記憶容量(数kB程度)のマクロを作っておき、これを複数個組み合わせることで所望のサイズのメモリを実現する。 |

| [用語4] | TOPS、TOPS/W:TOPSはtera operation per secondの略で、1秒当たりの演算数を意味する。TOPS/WはTOPSを電力で割った指標で、エネルギー当たりの演算数に相当し、エネルギー効率を表す。これらの指標はNNアクセラレータの性能評価の指標として用いられる。 |

- 論文情報

| 掲載誌: | IEEE Journal on Exploratory Solid-State Computational Devices and Circuits |

|---|---|

| タイトル: | Binarized Neural-Network Parallel-Processing Accelerator Macro Designed for an Energy Efficiency Higher Than 100 TOPS/W |

| 著者: | Yusaku Shiotsu, and Satoshi Sugahara |

| DOI: | 10.1109/JXCDC.2025.3538702 |

関連リンク

お問い合わせ

東京科学大学 総合研究院

未来産業技術研究所

准教授 菅原 聡

E-mail : sugahara@isl.titech.ac.jp

Tel/Fax : 045-924-5456

東京科学大学 総合研究院

未来産業技術研究所

博士研究員 塩津 勇作

E-mail : y.shiotsu@isl.titech.ac.jp

Tel/Fax : 045-924-5456