Electrical and Electronic Engineering News

Transforming small satellites for a bigger impact using an advanced wireless chip

A novel CMOS chip-based phased-array receiver maximizes satellite performance by supporting dual-polarized beams

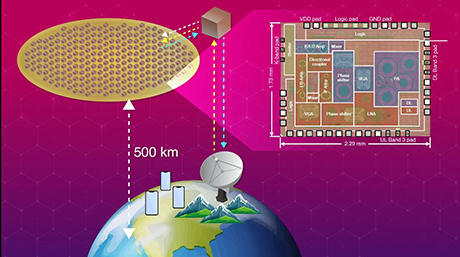

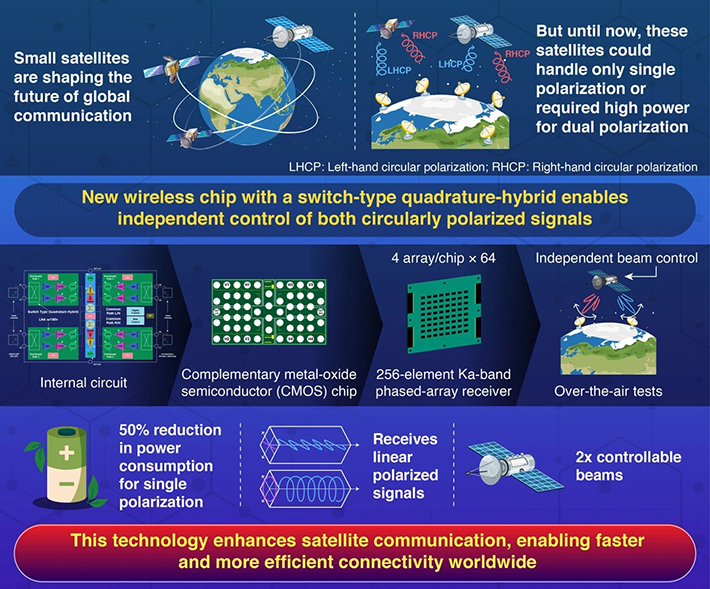

A first-of-its-kind 256-element Ka-band phased-array receiver, designed at Institute of Science Tokyo, Japan, can control two circular polarization beams independently, revolutionizing satellite communications with greater energy efficiency and better performance. Introduction of a novel switch-type quadrature-hybrid in the CMOS chip of the receiver effectively doubles the number of controllable beams, paving the way for enhanced data throughput and broader satellite coverage.

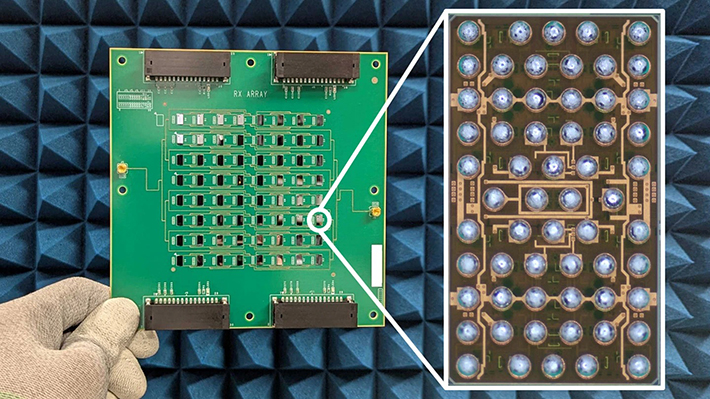

256-element Ka-band phased-array receiver developed by Institute of Science Tokyo

A CMOS chip with an integrated switch-type quadrature-hybrid and 4-array configuration, mounted on a 64-phase RX array to form a 256-element phased-array receiver (4 array/chip × 64)

The world is steadily moving towards seamless, global connectivity through satellite constellations. Small satellites—weighing up to 10 to 100 kgs—are further enhancing the connectivity with their flexibility and scalability. But the application of small satellites often faces a significant challenge in their ability to accept communication beams.

Satellites communicate using communication beams, which are electromagnetic waves. In some waves, the electric field rotates in a spiral, and these waves are called circularly polarized beams. Based on the direction of the rotation, the beams can be either in right-hand circular polarization (RHCP) or in left-hand circular polarization (LHCP). Small satellites weighing in the 10s of kgs can only handle single polarization beams, whereas bulkier satellites often require higher power to handle both polarized beams.

Driven by this need, a team led by Associate Professor Atsushi Shirane at Tokyo Institute of Technology, which was integrated into Institute of Science Tokyo, Japan, has successfully developed a novel Ka-band wireless chip for small satellite communication systems that can independently control the two circularly polarized beams—a property that was unachievable with conventional technologies.

The research was carried out in collaboration with Axelspace, Japan, and the findings were presented at the 2025 International Solid-State Circuits Conference, held from February 16–20, 2025, at the San Francisco Marriott Marquis in California.

“Conventional satellite communication receivers often struggle to handle both RHCP and LHCP beams independently,” explains Shirane. “To overcome this, we designed a switch-type quadrature-hybrid within a wireless chip that can pick up both left-hand and right-hand circularly polarized signals.”

A quadrature-hybrid is a special circuit that splits a signal into two parts, with one part delayed slightly to create a 90-degree phase difference. It breaks a circularly polarized signal into two straight signals and allows the chip to compare them. This helps to determine whether the signal was spinning left or right and therefore enables it to recognize both types of polarization used in satellite communication.

The ability to independently steer both types of circularly polarized beams allows for greater communication flexibility, which is a critical requirement for satellite-based networks, especially as demand surges for broadband access in underserved and remote areas. Moreover, this innovation also doubled the number of controllable beams the satellite could handle, significantly improving the system’s capacity.

One notable benefit is that the chip has been fabricated using the widely adopted complementary metal-oxide-semiconductor (CMOS), which is a low-power, fast, and compact technology used to build integrated circuits. This adds to the cost-effectiveness and scalability of the receiver, which is crucial for real-world deployments.

“Our receiver chip works in Ka-band frequency, known for its high-speed data transfer,” emphasizes Shirane. “In fact, it’s the very same frequency band harnessed by cutting-edge satellite networks like SpaceX’s Starlink!”

To verify its performance, the receiver chip was tested within a prototype satellite-mounted communication device and was subjected to over-the-air measurements. This confirmed the chip’s performance in handling circular polarization beams while maintaining the fundamental requirements for satellite communication systems.

The technology is a fundamental leap forward for global connectivity and is expected to have a profound impact on satellite communication infrastructure. Further developments could enable broader high-speed connections, offering coverage across vast geographic areas that were previously unreachable.

In an increasingly connected world, this innovation marks a new chapter for satellite-based communication—one that promises to bridge digital divides and make global communication efficient, affordable, and accessible for all.

Doubling Communication Beams for Small Satellite Networks

A 256-Element Ka-Band CMOS Phased-Array Receiver Using Switch-Type Quadrature-Hybrid-First Architecture for Small Satellite Constellations![]()

Kato et al. (2025) | 2025 International Solid-State Circuits Conference | DOI:10.1109 / ISSCC49661.2025.10904607

- Reference

| Authors: | Sena Kato1, Jill Mayeda1, Keito Yuasa1, Michihiro Ide1, Takeshi Ota1, Shu Date1, Yudai Yamazaki1, Xiaolin Wang1, Xi Fu1, Dongwon You1, Makoto Higaki2, Jumpei Sudo2, Hiroshi Takizawa2, Masashi Shirakura2, Takashi Tomura1, Hiroyuki Sakai1, Kazuaki Kunihiro1, Kenichi Okada1, and Atsushi Shirane1 |

|---|---|

| Title: | A 256-Element Ka-Band CMOS Phased-Array Receiver Using Switch-Type Quadrature-Hybrid-First Architecture for Small Satellite Constellations |

| Journal: | 2025 IEEE International Solid-State Circuits Conference (ISSCC) |

| DOI: |

10.1109/ISSCC49661.2025.10904607 |

| Affiliations: |

1Tokyo Institute of Technology, Tokyo, Japan 2Axelspace, Tokyo, Japan |

Related articles

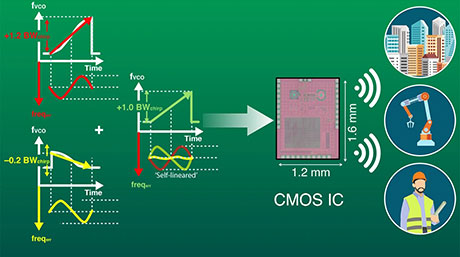

- Wirelessly Powered Relay Will Help Bring 5G Technology to Smart Factories | Former Tokyo Tech

- Towards Wider 5G Network Coverage: Novel Wirelessly Powered Relay Transceiver | Former Tokyo Tech

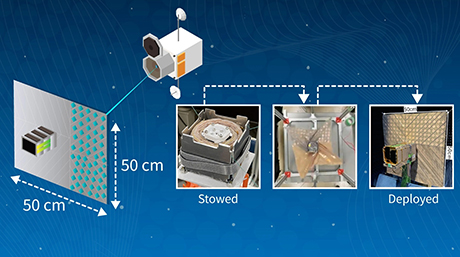

- Towards the New-Space Era with Foldable Phased-Array Transmitters for Small Satellites | Former Tokyo Tech

- New Transmitter Design for Small Satellite Constellations Improves Signal Transmission | Former Tokyo Tech

- Improving the Performance of Satellites in Low Earth Orbit | Former Tokyo Tech

- Atsushi Shirane | Researcher Finder - Science Tokyo STAR Search

- Takashi Tomura | Researcher Finder - Science Tokyo STAR Search

- Kenichi Okada | Researcher Finder - Science Tokyo STAR Search

- Shirane Laboratory

- Tomura Laboratory

- Okada Laboratory

- Laboratory for Future Interdisciplinary Research of Science and Technology

- Electrical and Electronic Engineering Graduate Major | Education | Department of Electrical and Electronic Engineering

- Electrical and Electronic Engineering Undergraduate Major | Education | Department of Electrical and Electronic Engineering

- School of Engineering | Science Tokyo

Further information

Associate professor Atsushi Shirane

Laboratory for Future Interdisciplinary Research of Science and Technology, Institute of Integrated Research, Institute of Science Tokyo

E-mail : shirane@ee.e.titech.ac.jp