Electrical and Electronic Engineering News

A more accurate, low-cost 39 GHz beamforming transceiver for 5G communications

Researchers at Tokyo Tech and NEC Corporation, Japan, present a 39 GHz transceiver with built-in calibration for fifth-generation (5G) applications. The advantages to be gained include better quality communications as well as cost-effective scalability.

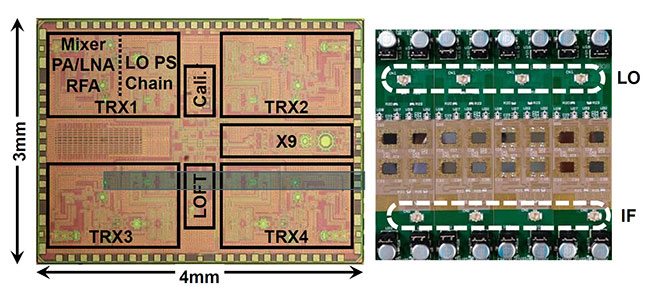

CMOS chips on an 18 mm x 163.5 mm evaluation-board

A team of more than 20 researchers at Tokyo Tech and NEC Corporation has successfully demonstrated a 39 GHz transceiver that could be used in the next wave of 5G wireless equipment including base stations, smartphones, tablets and Internet-of-Things (IoT) applications.

Although research groups including the current team have until now largely focused on developing 28 GHz systems, 39 GHz will be another important frequency band for realizing 5G in many parts of the world.

The new transceiver (shown in Figure 1) is based on a 64-element (4 x 16) phased-array1 design. Its built-in gain phase calibration means that it can improve beamforming2 accuracy, and thereby reduce undesired radiation and boost signal strength.

Figure 1. A micrograph of the chip and the 64-element module

The transceiver, based on a 64-element phased-array design, takes up a chip area of 12 mm2.

Fabricated in a standard 65-nanometer CMOS3 process, the transceiver's low-cost silicon-based components make it ideal for mass production — a key consideration for accelerated deployment of 5G technologies.

The researchers showed that the built-in calibration has a very low root-mean-square (RMS) phase error of 0.08°. This figure is an order of magnitude lower than previous comparable results. While transceivers developed to date typically suffer from high gain variation of more than 1 dB, the new model has a maximum gain variation of just 0.04 dB over the full 360◦ tuning range.

"We were surprised to achieve such a low gain variation when actually using the calibration based on our local-oscillator (LO) phase-shifting approach," says project leader, Kenichi Okada of Tokyo Tech.

In addition, the transceiver has a maximum equivalent isotropic radiated power (EIRP)4 of 53 dBm. This is an impressive indication of the output power of the 64 antennas, the researchers say, particularly for low-cost CMOS implementation.

Indoor testing (under anechoic chamber conditions5), which involved a one-meter, over-the-air measurement, demonstrated that the transceiver supports wireless transmission of a 400 MHz signal with 64QAM.

"By increasing the array scale, we can achieve greater communication distance," Okada says. "The challenge will be to develop the transceiver for use in smartphones and base stations for 5G and beyond."

The work is being presented at the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC)![]() in Boston, Massachusetts, US, as part of the morning session (Session RTu2E) to be held on 4 June 2019. The paper of this work "A 39 GHz 64-Element Phased-Array CMOS Transceiver with Built-in Calibration" by Yun Wang et al., receives the best student paper award.

in Boston, Massachusetts, US, as part of the morning session (Session RTu2E) to be held on 4 June 2019. The paper of this work "A 39 GHz 64-Element Phased-Array CMOS Transceiver with Built-in Calibration" by Yun Wang et al., receives the best student paper award.

Referring to an electrically steerable array of antennas.

A powerful signal processing technique used to control antenna patterns.

Complementary metal–oxide–semiconductor, the main processing method for creating integrated circuits.

4 Equivalent isotropic radiated power (EIRP)

A measure of the signal strength or output power of an antenna in decibels per meter (dBm).

A non-reflective environment that is designed to be free from echoes.

Reference

| Authors : | Yun Wang1, Rui Wu1, Jian Pang1, Dongwon You1, Ashbir Aviat Fadila1, Rattanan Saengchan1, Xi Fu1, Daiki Matsumoto1, Takeshi Nakamura1, Ryo Kubozoe1, Masaru Kawabuchi1, Bangan Liu1, Haosheng Zhang1, Junjun Qiu1, Hanli Liu1, Wei Deng1, Naoki Oshima2, Keiichi Motoi2, Shinichi Hori2, Kazuaki Kunihiro2, Tomoya Kaneko2, Atsushi Shirane1, Kenichi Okada1 |

|---|---|

| Session : | Session RTu2E |

| Session title : | A 39GHz 64-Element Phased-Array CMOS Transceiver with Built-in Calibration |

| Conference : | |

| Affiliations : |

1Department of Physical Electronics, Tokyo Institute of Technology 2NEC Corporation |

- Gearing up for 5G: A miniature, low-cost transceiver for fast, reliable communications | Tokyo Tech News

- Tinier and less power-hungry quantum atomic clock push toward intelligent IoT | Tokyo Tech News

- An ultra-low-power frequency synthesizer targeted for IoT devices: Digital PLL achieves a power consumption of 0.265 mW | Tokyo Tech News

- Tokyo Tech slashes power consumption in Bluetooth Low-Energy transceiver by more than half | Tokyo Tech News

- New 28-GHz transceiver paves the way for future 5G devices | Tokyo Tech News

- Ultra high-speed IC capable of wireless transmission of 100 gigabits per second in a 300 GHz band | Tokyo Tech News

- Speeding up adoption of 5G! Wireless transmission speeds of 120 Gbps achieved | Tokyo Tech News

- 28Gb/s wireless data rate achieved with millimeter-wave transceiver | Tokyo Tech News

- Kenichi Okada - Wiring the world wirelessly | Research Stories | Research

- Matsuzawa and Okada Laboratory won NE Analog Innovation Award | Electrical and Electronic Engineering News

- Okada Lab.

- Researcher Profile | Tokyo Tech STAR Search - Atsushi Shirane

- Researcher Profile | Tokyo Tech STAR Search - Kenichi Okada

- NEC Corporation

- Latest Research News

School of Engineering

—Creating New Industries and Advancing Civilization—

Information on School of Engineering inaugurated in April 2016

Further Information

Professor Kenichi Okada

School of Engineering, Tokyo Institute of Technology

Email okada@ee.e.titech.ac.jp

Tel +81-3-5734 -3764