Electrical and Electronic Engineering News

Pushed to the Limit: A CMOS-based transceiver for beyond 5G applications at 300 GHz

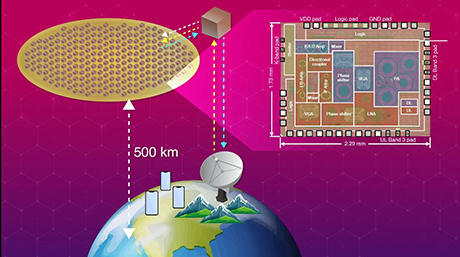

Scientists at Tokyo Institute of Technology and NTT Corporation develop a novel CMOS-based transceiver for wireless communications at the 300 GHz band, enabling future beyond-5G applications. Their design addresses the challenges of operating CMOS technology at its practical limit and represents the first wideband CMOS phased-array system to operate at such elevated frequencies.

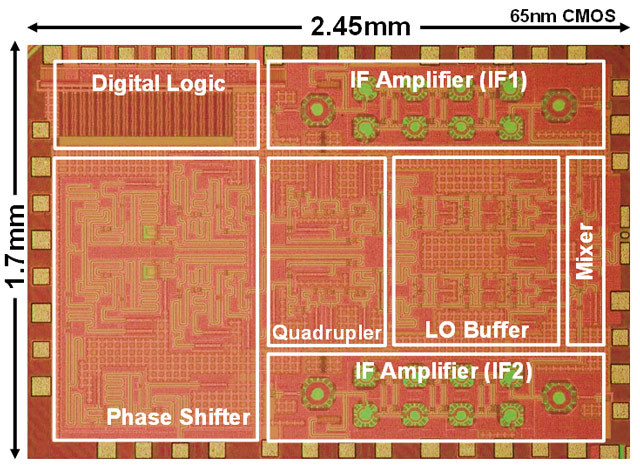

Figure 1. Chip micrograph of 300 GHz-band phased-array transceiver implemented by 65 nm CMOS

Communication at higher frequencies is a perpetually sought-after goal in electronics because of the greater data rates that would be possible and to take advantage of underutilized portions of the electromagnetic spectrum. Many applications beyond 5G, as well as the IEEE802.15.3d standard for wireless communications, call for transmitters and receivers capable of operating close to or above 300 GHz.

Unfortunately, our trusty CMOS technology is not entirely suitable for such elevated frequencies. Near 300 GHz, amplification becomes considerably difficult. Although a few CMOS-based transceivers for 300 GHz have been proposed, they either lack enough output power, can only operate in direct line-of-sight conditions, or require a large circuit area to be implemented.

To address these issues, a team of scientists from Tokyo Institute of Technology (Tokyo Tech), in collaboration with NTT Corporation (NTT), proposed an innovative design for a 300 GHz CMOS-based transceiver (Figure 1). Their work will be presented in the Digests of Technical Papers in the 2021 IEEE ISSCC (International Solid-State Circuits Conference), a conference where the latest advances in solid-state and integrated circuits are exposed.

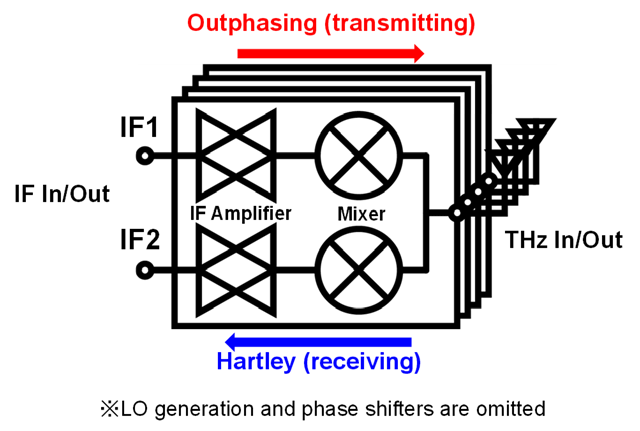

One of the key features of the proposed design is that it is bidirectional; a great portion of the circuit, including the mixer, antennas, and local oscillator, is shared between the receiver and the transmitter (Figure 2). This means the overall circuit complexity and the total circuit area required are much lower than in unidirectional implementations.

Figure 2. Proposed bidirectional phased-array transceiver architecture

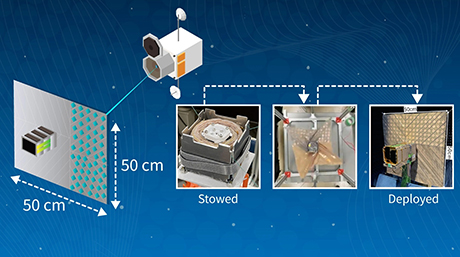

Another important aspect is the use of four antennas in a phased array configuration. Existing solutions for 300 GHz CMOS transmitters use a single radiating element, which limits the antenna gain and the system's output power. An additional advantage is the beamforming capability of phased arrays, which allows the device to adjust the relative phases of the antenna signals to create a combined radiation pattern with custom directionality. The antennas used are stacked "Vivaldi antennas," which can be etched directly onto PCBs, making them easy to fabricate.

The proposed transceiver uses a subharmonic mixer, which is compatible with a bidirectional operation and requires a local oscillator with a comparatively lower frequency. However, this type of mixing results in low output power, which led the team to resort to an old yet functional technique to boost it. Professor Kenichi Okada from Tokyo Tech, who led the study, explains: "Outphasing is a method generally used to improve the efficiency of power amplifiers by enabling their operation at output powers close to the point where they no longer behave linearly—that is, without distortion. In our work, we used this approach to increase the transmitted output power by operating the mixers at their saturated output power." Another notable feature of the new transceiver is its excellent cancellation of local oscillator feedthrough (a "leakage" from the local oscillator through the mixer and onto the output) and image frequency (a common type of interference for the method of reception used).

The entire transceiver was implemented in an area as small as 4.17 mm2. It achieved maximum rates of 26 Gbaud for transmission and 18 Gbaud for reception, outclassing most state-of-the-art solutions. Excited about the results, Okada remarks: "Our work demonstrates the first implementation of a wideband CMOS phased-array system that operates at frequencies higher than 200 GHz." Let us hope this study helps us squeeze more juice out of CMOS technology for upcoming applications in wireless communications!

- Reference

- Conference :

- 2021 IEEE International Solid-State Circuits Conference (ISSCC 2021)

- Session :

- Session 22.2: Terahertz for Communication and Sensing

February 17th 8:30 AM (PST) - Session Title :

- A 300GHz-Band Phased-Array Transceiver Using Bi-Directional Outphasing and Hartley Architecture in 65nm CMOS

[Technical paper are released at February 5 5:00 PM (PST), Live Q&As : February 17th 8:38 AM PST]

Proceedings of the 2021 IEEE ISSCC (International Solid-State Circuits Conference) - Authors :

- Ibrahim Abdo1, Carrel da Gomez1, Chun Wang1, Kota Hatano1, Qi Li1, Chenxin Liu1, Kiyoshi Yanagisawa1, Ashbir Aviat Fadila1, Jian Pang1, Hiroshi Hamada2, Hideyuki Nosaka2, Atsushi Shirane1, Kenichi Okada1

- Affiliations :

1 Tokyo Institute of Technology, Tokyo, Japan

2 NTT, Kanagawa, Japan

- Greater Connectedness in Remote Areas: A Ka-band Transceiver for Satellite Communications | Tokyo Tech News

- Smallest all-digital circuit opens doors to 5 nm next-gen semiconductor | Tokyo Tech News

- A more accurate, low-cost 39 GHz beamforming transceiver for 5G communications | Tokyo Tech News

- An ultra-low-power frequency synthesizer targeted for IoT devices: Digital PLL achieves a power consumption of 0.265 mW | Tokyo Tech News

- Tinier and less power-hungry quantum atomic clock push toward intelligent IoT | Tokyo Tech News

- Gearing up for 5G: A miniature, low-cost transceiver for fast, reliable communications | Tokyo Tech News

- New 28-GHz transceiver paves the way for future 5G devices | Tokyo Tech News

- Ultra high-speed IC capable of wireless transmission of 100 gigabits per second in a 300 GHz band | Tokyo Tech News

- Tokyo Tech slashes power consumption in Bluetooth Low-Energy transceiver by more than half | Tokyo Tech News

- Speeding up adoption of 5G! Wireless transmission speeds of 120 Gbps achieved | Tokyo Tech News

- Prof. Kenichi Okada awarded the 18th DOCOMO Mobile Science Award | Tokyo Tech News

- Kenichi Okada - Wiring the world wirelessly | Research Stories | Research

- Okada Lab.

- Researcher Profile | Tokyo Tech STAR Search - Kenichi Okada

- Researcher Profile | Tokyo Tech STAR Search - Atsushi Shirane

- Electrical and Electronic Engineering Graduate Major|Education|Department of Electrical and Electronic Engineering, School of Engineering

- NTT R&D

- Latest Research News

School of Engineering

—Creating New Industries and Advancing Civilization—

Information on School of Engineering inaugurated in April 2016

Further Information

Prof. Kenichi Okada

School of Engineering, Tokyo Institute of Technology

Email okada@ee.e.titech.ac.jp

Tel +81-3-5734 -3764