電気電子系 News

極低消費電力のデジタル位相同期回路を開発

IoT社会を支える電子部品

要点

- 電子機器に組み込むデジタル位相同期回路[用語1]の低消費電力化を実現

- サブサンプリングとサンプリングを組み合わせて従来よりも60%の電力削減を実現

- エネルギー効率を重視するSoCなどへの応用を期待

概要

東京工業大学 工学院 電気電子系の岡田健一准教授らの研究グループは、極低消費電力で動作する分数分周タイプ[用語2]のデジタル位相同期回路(PLL、phase locked loop)の開発に成功した。これは、PLLの通常のサンプリング動作にサブサンプリング動作[用語3]を組み合わせることで実現した。これまでサブサンプリング動作により低消費電力化が可能な反面、稀に誤った周波数を出力する問題があった。それを動作時間の短い周波数同期回路を用いることで問題を解決した。

開発したPLLは、最小の配線半ピッチ(幅)65 nm(ナノメートル)のシリコンCMOSプロセス[用語4]で試作し、265 μWの極低消費電力で動作することを確認した。これまでに報告された分数分周タイプのデジタルPLLに比べ、60%の消費電力削減を実現。このPLLは、エネルギー効率を重視するSoC[用語5]などのシステムへの応用が期待される。

研究成果は、2月17日~21日に米国サンフランシスコで開催される「ISSCC 2019(国際固体素子回路会議)」で発表される。

本研究開発の成果の一部は国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)委託事業「IoT推進のための横断技術開発プロジェクト」の結果得られたものである。

研究の背景・意義

昨今の高いエネルギー効率を目指すSoCなどのシステムにおいて、低消費電力CMOSの大規模集積回路(LSI)技術の重要性は高まりつつある。特にPLLは、例えば通信分野のキャリア生成やプロセッサ、メモリ等へのシステムクロックの生成など多岐にわたり必須の回路であり、性能を維持したまま低消費電力化する技術が不可欠だ。

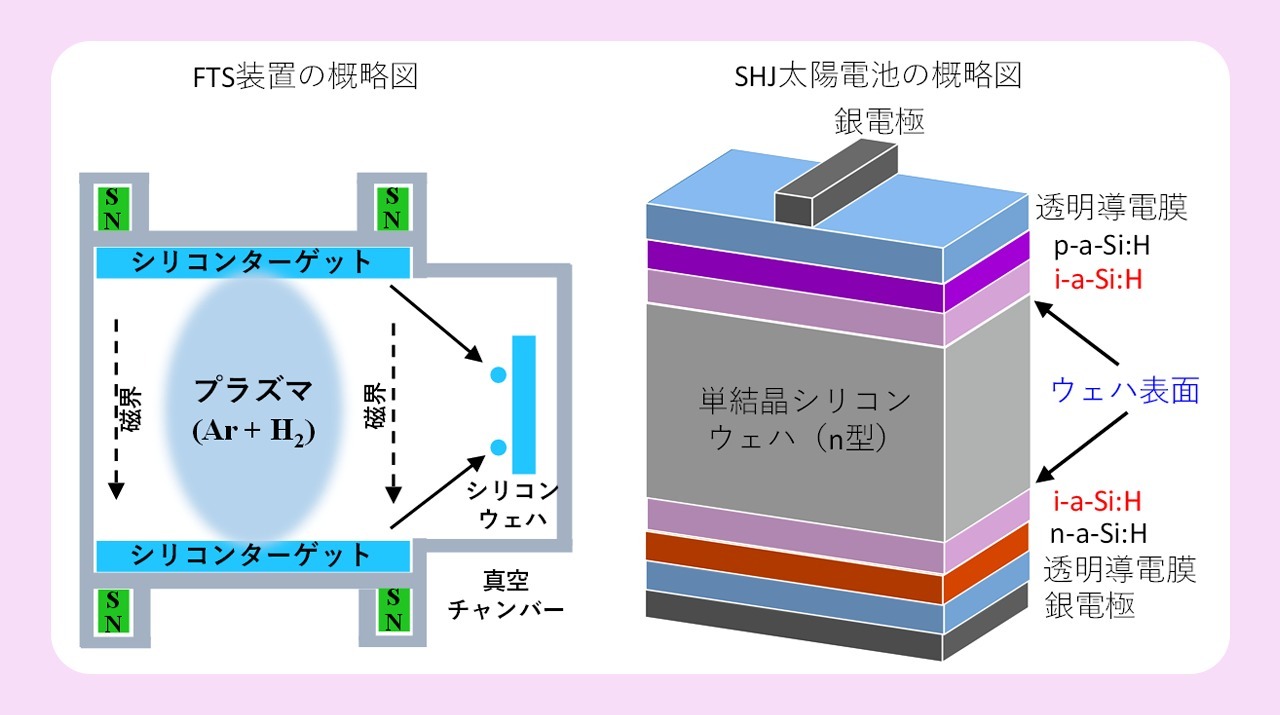

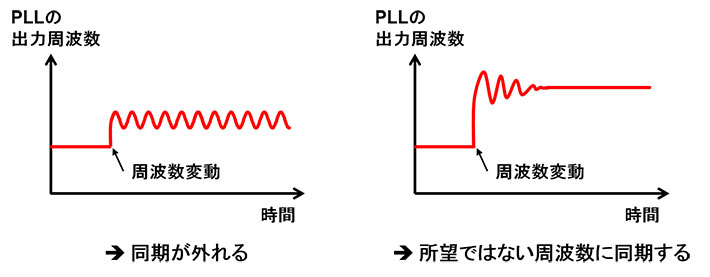

分数分周タイプのデジタルPLLは、PLL自身の低消費電力化や小面積化などを期待されこれまで多くの検討がなされているが、いまだ500 μW未満の動作消費電力は、実現されていなかった。近年、PLLの低消費電力化、低ジッタ化を図るサブサンプリング技術の応用も提案されているが、ノイズなどによる出力周波数変動で、PLLが同期から外れてしまう、あるいは出力周波数がリファレンス周波数の整数倍異なる周波数に同期してしまうなど誤動作が生じやすいことが課題となっている。誤動作は、周波数同期回路(FLL、frequency locked loop)をPLL内に実装することで、サブサンプリング動作中のPLLの周波数を常時モニタすることで回避できるが、FLLは常時動作しているためにPLLの消費電力の増大を招くことになる。(図1)

図1. サブサンプリングPLLの誤動作の例

研究成果

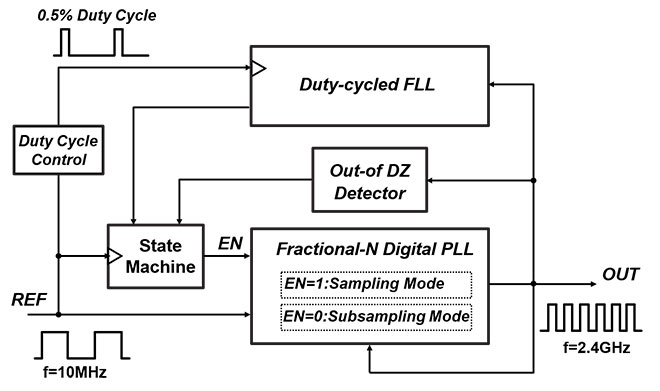

開発したデジタルPLLは、サブサンプリング動作とサンプリング動作を組み合わせることで低消費電力化とPLLの誤動作回避を両立している。図2に提案するPLLの概念図を示す。サンプリング動作時にPLLの周波数がリファレンス周波数REFに同期すると、PLLの動作モードは消費電力の少ないサブサンプリング動作に切り替わる。このサブサンプリング動作時の誤動作を解消するため、PLLにはODZ検出回路[用語6]とFLLが実装されている。ODZ検出回路はPLLの同期が外れた状態を検出し、PLLの動作モードを自動的にサンプリング動作に切り替える。また、FLLは、PLLが所望ではない周波数に同期した状態を検出し、PLLの動作モードをサンプリングモードに切り替える。通常のFLLは常にエネルギーを消費するため消費電力増大を招くが、本提案ではFLL内のカウンタの動作デューティ比[用語7]を0.5%にまで低下させるFLLの間欠動作を実現し、消費電力削減を実現した。通常のFLLを用いたサブサンプリングPLLと比較し、開発したPLLはサブサンプリング動作時の消費電力をおよそ70%削減できることがシミュレーションで確認されている。

図2. 提案する分数分周タイプのデジタル位相同期回路のブロック図

サブサンプリングとサンプリングの組み合わせ技術に加えて、ここではデジタルPLLの要素回路であり、通常PLL全体の消費電力の大部分を占めるデジタル制御発振器(DCO)[用語8]とデジタル時間変換器(DTC)[用語9]の低消費電力化も実現した。これはPLL全体の動作時消費電力の削減に貢献している。

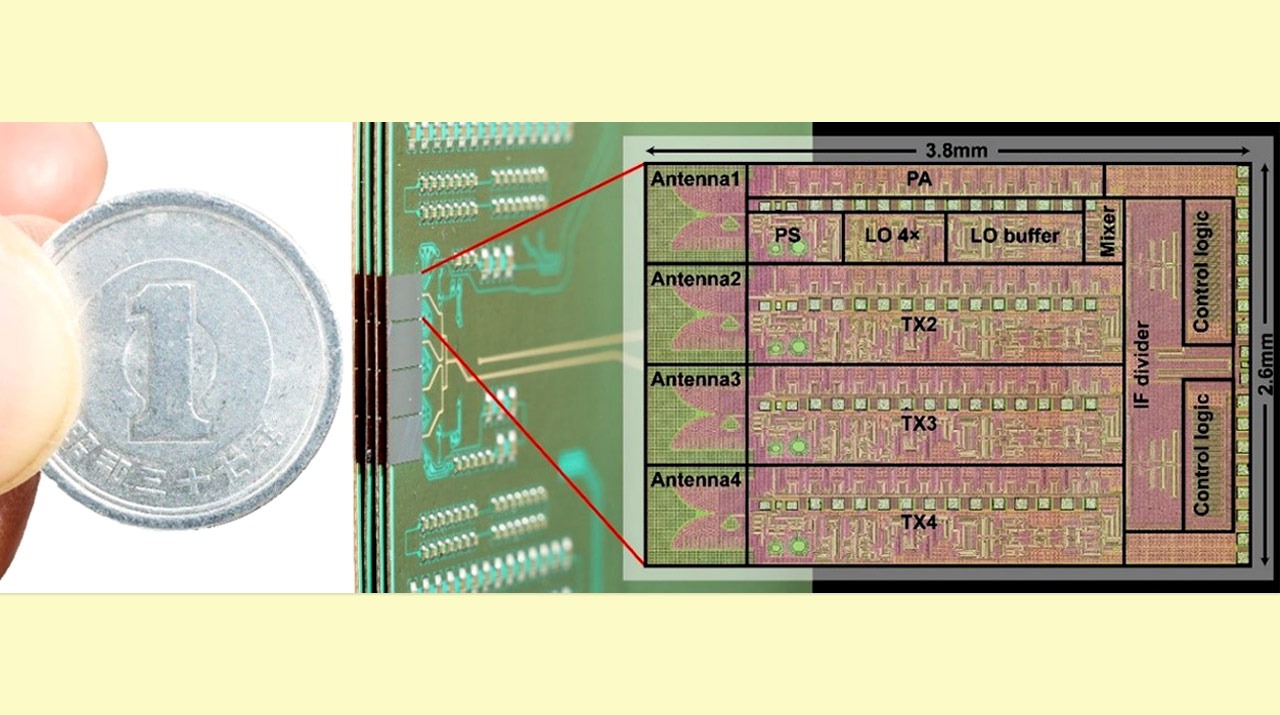

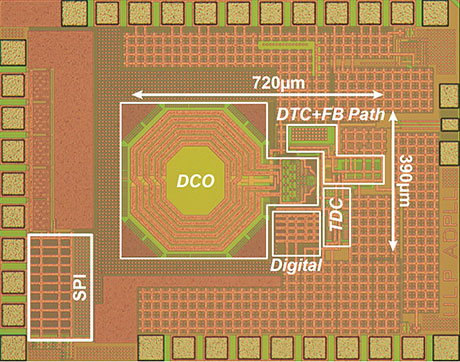

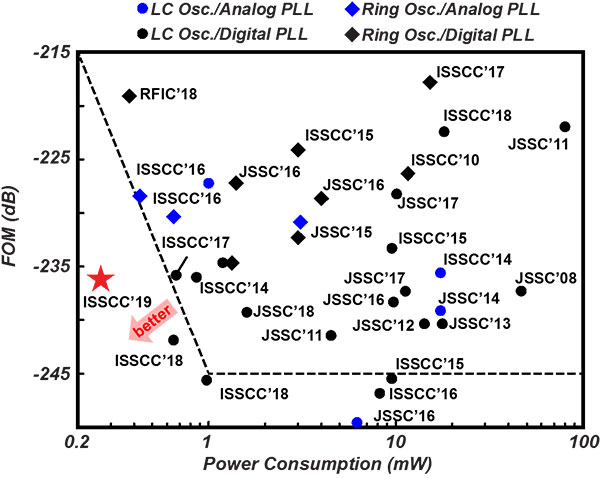

提案する分数分周デジタルPLL回路は図3に示すように最小配線半ピッチ(幅)65 nmのシリコンCMOSプロセスで試作された。PLLの性能要約を表1に示す。試作されたPLLは10 MHzのリファレンス周波数から2.05~3.10 GHzの出力周波数を生成する。動作時の消費電力は265 μWであり、これまでに報告されている分数分周デジタルPLLの中で最も低消費電力である。またPLLのジッタ特性[用語10]を表すFoM[用語11]でも-236.8 dBという良好な値を達成した。図4に提案するPLL及び先行研究にて提案されたPLLの、動作時の消費電力に対するFOMを示す。一般的にPLLのジッタ特性と消費電力はトレードオフの関係にあるが、提案するPLLはジッタ特性を維持したまま、つまり出力信号の品質を維持したまま低消費電力化を実現していることを実証した。

図3. 開発したPLLのチップ写真

表1. 開発したPLLの性能要約

| This Work | ISSCC'17 | ISSCC'14 | ISSCC'18 | |

|---|---|---|---|---|

| Output Frequency (GHz) | 2.20 - 2.80 | 1.8 - 2.5 | 2.1 - 2.7 | 2.0 - 2.8 |

| Power (μW) | 265 | 673 | 860 | 980 |

| FoM (dB) | -236.8 | -235.8 | -236 | -245.6 |

図4. PLLのFoM vs. 消費電力

今後の展開

本研究で開発されたデジタルPLLは高いエネルギー効率を必要とするアプリケーションの実現に貢献すると期待される。例えば、近年広がりを見せるIoT(モノのインターネット)においては、近い将来にIoT機器の個数が1兆個にも及ぶと予測している。多くのIoT機器は電池などの電源が必要で、その中で、いかに電池の寿命を延命し電池交換のメンテナンスコストを低下させるかがIoT社会の実現の鍵を握っている。現状のIoT機器は通信時に最も電力を使い、その通信回路の中でもPLLは消費電力の大部分を占める。開発した超低消費電力PLLを適用することで、例えば、3 mW程度の消費電力であるレシーバの消費電力は約半分程度になると予想される。

発表予定

この成果は2月17日~21日にサンフランシスコで開催される「2019 IEEE International Solid-State Circuits Conference (ISSCC 2019) : 2019年米国電気電子学会 国際固体素子回路会議」における講演セッション「Session 16 – Frequency Synthesizers」において、「A 265 μW Fractional-N Digital PLL with Seamless Automatic Switching Subsampling/Sampling FeedBack Path and Duty-Cycled Frequency-Locked Loop in 65 nm CMOS (265 μWで動作する分数分周デジタルPLL)」の講演タイトルで、現地時間2月19日午後1時30分から発表する。

講演

| 講演セッション : | Session 16 –Frequency Synthesizers |

|---|---|

| 講演時間 : | 現地時間2月19日午後1時30分 |

| 講演タイトル : | A 265μW Fractional-N Digital PLL with Seamless Automatic Switching Subsampling/Sampling FeedBack Path and Duty-Cycled Frequency-Locked Loop in 65nm CMOS (265 μWで動作する分数分周デジタルPLL) |

| ISSCC会議情報 : |

用語説明

[用語1] 位相同期回路 (PLL : Phase-Locked Loop) : 集積回路中では正確な周波数基準が作れないため、水晶発振器による基準周波数frefを用い、それをN逓倍して所望周波数N・frefの周波数の信号を得る。PLLには、位相周波数比較器、チャージポンプ、ローパスフィルタを用いるアナログPLLと、時間差デジタル変換器(TDC)とデジタルローパスフィルタを用いるデジタルPLL(オールデジタルPLLとも呼ばれる)が知られている。

[用語2] 分数分周PLL : PLLには、整数分周型と分数分周型がある。整数分周型PLLでは基準信号に対して整数倍の周波数を出力するが、分数分周型では分数倍の任意の周波数の出力が可能である。例えば、水晶発振器から入力される基準クロック周波数が26 MHzの場合、整数分周PLLでは2,418 MHz(93倍)、2,444 MHz(94倍)、2,470 MHz(95倍)の生成が可能であるが、分数分周PLLでは2,442 MHz(93.923倍)のような任意の小数精度の逓倍動作が可能である。BLE等の無線通信用には、整数分周型ではなく分数分周型のPLLが必要である。アナログPLLでは分数分周型を比較的容易に実現できるが、低消費電力化で有利なデジタルPLLにおいて分数分周型のものはジッタ特性が劣化しやすく実現が難しい。

[用語3] PLLのサブサンプリング動作 : 周波数逓倍器を介さないループにより位相を同期させるPLLの動作。通常のPLLのサンプリング動作と比較してPLLの出力信号は周波数逓倍器によるノイズの影響を受けないために高精度化が望めるが、水晶発振器による基準周波数frefをN逓倍した所望周波数N・frefの周波数の信号を得るためにFLLが必要となる。

[用語4] CMOSプロセス : N型とP型のMOSFETを相補的に用いた集積回路であり、バイポーラプロセスと比較し消費電力の削減と高い集積率を実現したプロセスである。近年の集積回路はほぼCMOSプロセスとなっている。

[用語5] SoC(System on Chip) : プロセッサやメモリ、その他システムを実現するために必要となるすべての回路が集積された集積回路。

[用語6] ODZ(Out-of-deadzone)検出回路 : PLLが同期した状態とはPLLへの基準信号とPLL内信号の位相偏差ΔΦが小さくなり、PLLの不感帯(deadzone)に収束した状態を指す。ΔΦが不感帯より外れるとPLLループの負帰還が働きΔΦは不感帯内に収束する。本提案PLLはΔΦが不感帯内にある場合サブサンプリング動作を行い、Φが不感帯から外れるとサンプリング動作を行うが、この動作モードの切り替えのためにΔΦが不感帯から外れた状態を検出するOut-of-deadzone検出回路が必要となる。

[用語7] 動作デューティ比 : 必要時のみ動作しそれ以外の時間は待機状態にある間欠動作をする回路に関して、動作している時間と待機状態にある時間の比を示す。一般的な回路は動作時に待機時以上の電力を消費することから、この動作デューティ比を低下させることが回路の消費電力低下につながる。

[用語8] デジタル制御発振器 (DCO :Digitally Controlled Oscillator) : デジタル制御値により発振周波数が変化する発振回路。PLLの発振周波数とリファレンス周波数の偏差に応じてDCOに与えるデジタル制御値が決まり、偏差を低下させるようにDCOの発振周波数は変化する。PLLの出力周波数はDCOの発振周波数と一致する。

[用語9] デジタル時間変換器 (DTC : Digital-to-Time Converter) : デジタル制御値により、遅延時間が変化する可変遅延回路。デジタル制御遅延回路(DCDL, Digitally-Controlled Delay Line)とも呼ばれる。PLLなどの幅広い回路で利用されている。

[用語10] ジッタ特性 : クロックの重要な特性の一つで、クロック信号の立ち上がりまたは立ち下りタイミングが揺らぐ現象で、本来のタイミングからのずれが統計的にどれぐらいの幅を持つかで評価する。ジッタが小さいほど、クロックの揺らぎが小さい状況を示す。クロックを生成している発振器の位相雑音特性に大きく依存し、位相雑音が低いほど、ジッタも小さくなる。

[用語11] FoM : FoM(Figure of Merit)の略で、消費電力で規格化したジッタ性能を示す。ジッタと消費電力はトレードオフの関係にあり、発振器の消費電力を増やすとジッタが減少し、消費電力を減らすとジッタが増加する。

FoMは、ジッタの標準偏差(σt)と消費電力PDCを用いて、以下の式で定義される。

![]()

ジッタ特性が同じでFoMが10 dB小さければ、消費電力が10分の1であることに相当する。

- 超省エネ・小型の原子時計の開発に成功│東工大ニュース

- 5G向けミリ波無線機の省面積化に成功│東工大ニュース

- 世界最小電力で動作するBLE無線機を開発│東工大ニュース

- 5G向けミリ波無線機の小型化に成功│東工大ニュース

- 300 GHz帯で毎秒100ギガビットの無線伝送が可能な超高速ICを開発│東工大ニュース

- 水晶発振回路の高速起動化でIoT機器の消費電力を大幅低減│東工大ニュース

- 世界最高速!毎秒120ギガビットの無線伝送に成功│東工大ニュース

- 新型デジタル発振器を開発 ―電圧サブサンプリングにより低消費電力、低ジッタ実現―│東工大ニュース

- 東工大教員3名が平成29年度科学技術分野の文部科学大臣表彰で「科学技術賞」を受賞│東工大ニュース

- いつか、有線を超える無線技術を夢見て~ミリ波から広がる世界最速の無線機への可能性~ ― 岡田健一│研究ストーリー|研究

- 松澤・岡田研究室―日経エレクトロニクスからNEアナログ・イノベーション・アワード優秀賞を受賞|電気電子系 News

- 松澤・岡田研究室 ―研究室紹介 #1―│電気電子系 News

- 岡田研究室

- 研究者詳細情報(STAR Search) - 岡田健一 Kenichi Okada

- 研究成果一覧

お問い合わせ先

東京工業大学 工学院 電気電子系

岡田健一 准教授

E-mail : okada@ee.e.titech.ac.jp

Tel : 03-5734-3764 / Fax : 03-5734-3764